2.8 Command Console for Interactive Debugging |

|

|

|

2.8 Command Console for Interactive Debugging |

|

|

BugHunter has an interactive command console for entering simulator commands to observe, control, and debug a simulation. For example, during an interpreted Verilog simulation, you can enter a Verilog command such as $finish; (to end the simulation) or $display; (to display the value of a variable). The command console is used to enter commands that are not available in a graphical environment. The types of commands that are supported are dependent on your particular simulator. BugHunter takes the commands and hands them directly to the simulator console. The console maintains a separate history of previously entered commands for each simulator, so that when you switch back and forth between different simulators, you will have a history of valid commands for the current simulator.

Set the Scope before using most Command Console Functions:

Most of the commands for the Console window are scope sensitive. Here are some quick tips on working with scopes:

•Find a component in your project and choose one of the Goto menus to set the scope to that level. This will also open an editor with the relevant code. |

|

•Press the CTRL-C keys to copy the full hierarchical name of a component. •The CTRL-V keys can be used to paste the name into text boxes, editors, search boxes, and the console window. |

|

To use the command console window:

•Stop the simulator during a simulation run by either (1) single stepping into the design, (2) hitting a breakpoint, (3) pressing the pause button, or (4) inserting a $stop system task into the code. When a simulation is stopped, the simulation display on the status bar turns bright green and displays the current simulation time and scoping level. |

![]()

•Type a command into the console window or pick one from the drop-down list and press the <Enter> key or the black arrow button. •The scope buttons change the scoping level for the commands in the console window. The "S" changes the scope to the top-level component. The "s" changes scope to the current simulation level. |

|

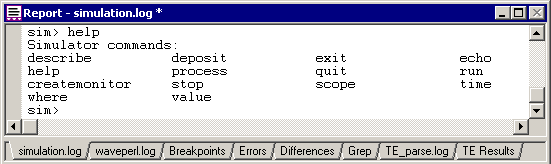

•Type the help command to retrieve a list of available commands for your simulator. BugHunter just passes the command to the simulator and there is not a standard list of commands that all simulators support. The list is displayed in the simulation.log tab of the Report window. |

|

•To get more information about a specific command, type help name_of_command. |

|

VeriLogger Extreme (simx) Console Commands:

createmonitor instance output [-r [level]] [--signals] [--variables]

Creates a monitor for signals/variables from a given instance. Monitor source will be saved into the specified output file.

•instance: Instance hierarchy path. May contain wildcards at the end. Wildcards are applied only to signal/variable items.

•-r [level]: Recursively monitors items from child instances. The level determines max nesting level. If not specified all child instances will be dumped.

•--signals: Dumps only signals (e.g. Verilog wires)

•--variables: Dumps only variables (e.g. Verilog registers)

•--ports: Dumps only ports

•--parameters: Dumps only parameters

•--compact: Dumps simulation results in compacted form

deposit <object-name> [=] <value>

Set the value of the given object unless it is forced or, in the case of registers, assigned.

•-after <time-spec> [[<value> -after <time-spec>]...]: Delay the assignment of the new value. Multiple values may be provided along with the time-specs

•[-absolute]: The given time is the time at which the assignment should occur

•[-relative]: The given time is a delay after which the assignment should occur

•-repeat <time-spec>: Repeat the assignment of the value after the specified time

•-cancel <time-spec>: Cancel the assignment of the value after the specified time

•-release: Release any existing force or procedural continuous assign on the object

•-inertial: Deposit value after an inertial delay

•-transport: Deposit value after a transport delay

describe <item-names>

For each item given, print a description of it

echo

Prints message to console log window

echo hello

exit

Exits the Tcl application

help [-all|-help|-h|<cmd_name>]

The command help with no options prints a list of the built-in simulator shell commands.

•-all: prints all the built-in and user registered commands

•-help or -h: prints the available options for the help option

•<cmd_name>: prints help information about the specified command

process

Show information on processes (behavioral blocks) that are currently executing or are scheduled to execute at the current simulation time

quit

Exits the Tcl application

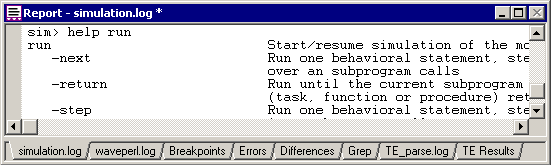

run

Start/resume simulation of the model

•-next: Run one behavioral statement, stepping over any subprogram call

•-return: Run until the current subprogram (task, function or procedure) returns

•-step: Run one behavioral statement, stepping into subprogram calls

•[-timepoint] <time-spec>: Run until the given time is reached

•-absolute: The given time is an absolute simulation time

•[-relative]: The given time is relative to the current time

•-no_source_text: Avoids HDL source printing during stepping

•-source_text <sibling_lines>: Specify number of sibling lines to be printed around currently debugged statement.

scope

List source or declared objects for a scope, or set the debug scope

•-describe [<scope-spec>]: Describe items declared within the given scope, or if no scope is given then within the current debug scope

•-names: Show only the names of each declared item

•[-set] [<scope-spec>]: Set the current debug scope to the given scope, or if no scope name or other option is given then print the name of the current scope. The -set may be omitted.

•-show: Shows useful scope information: current debug scope, instances within the debug scope, and top-level modules in the currently loaded model

•-tops: Lists the names of the top level scopes in the currently loaded model

stop

Create or operate on a stop

•-line <line-number>: Stop when the given line is about to be executed are instances of the same module.

•-file <file-name>: Specifies which of the source files that make up

•[-hitcount <hit-number>]: Specifies stop hit count

•-time <time-spec>: Stop when the simulation reaches the given time

•[-absolute]: Time specification is absolute - the stop will be deleted after this time is reached

•[-relative]: Time specification is an interval - the stop will be persistent and will occur repetitively with the given interval

•-object <object-names>: Stop when given object changes value

•[-value <value>]: Specifies value condition to allow breakpoint hit

•-delete <stop-names>: Delete the named stops

•-disable <stop-names>: Disable the named stops

•-enable <stop-names>: Enable the named stops

•-show [<stop-names>]: Show information on each named stop, or on all stops if no name is given

•-help Prints this message

time

Displays current simulation time

value [format] object_names

Print the current value of each named object using the last format seen before the object name on the command line (if none, a default format is used). Valid formats are: %c, %s, %b, %o, %h, %x, %d, %t, %v, %e, %f, %g. To revert to default format, use '%'

where

Displays the current location of simulation

Some VeriLogger Pro and Cadence Verilog XL commands:

Interpreted Verilog simulators such as VeriLogger Pro and VerilogXL can execute lines of Verilog behavioral code entered into the console window. These commands will not work with VeriLogger Extreme and other compiled simulators.

Generally, any behavioral statement used within an initial or always block can be entered into the console window. Statements that affect the project structurally, such as instantiating a model, are not allowed. All system tasks are accepted in the console window. Compiled code simulators can not do this because all code must be compiled before simulation begins.

Because all Verilog commands require a terminating semicolon, the semicolon must be entered in the console window. Below are some examples of useful interactive commands:

•For example: •To continue the simulation, type the period (.) character, or press the green Run button. •To step to the next statement in the code, type the semicolon (;) character, or press the Step Over button. •To step-and-trace (step to the next statement in the code and generate a trace message in the verilog.log file) type the comma (,) character, or press the Step Into button. •To display the current code-line execution, (open an editor window and display the currently executing line of HDL code) type the colon (:) character, or press the Goto button (the magnifying glass). •To terminate the simulation, type the $finish; command or press the red STOP button. •Displaying Variables: Use the $display(...); system task to view a variable's current value. Make sure that the scope is correct. A common mistake is to view a trace, pause the simulation, and type $display; without realizing that the variable may not be in the current scope. In interactive mode, the current scope is set using the scope buttons or the $scope system task. By default, the scope is set to the top-level component, not the scope at the current execution line. For example, the following statement could be used to view the variable ireg: $scope (top.cpu1.iunit); $display (ireg); // OR, this can be expressed as a single statement $display (top.cpu1.iunit.ireg); All the variables in a given scope can be displayed using the $showvars system task. $showvars also displays the information about when the variable was last modified, specifically, the simulation time, the file name, and the line number of the reference. •Changing Variables: Use an assignment statement to change a variable's value. ireg = 4 * bar; •Variable Watches (breakpoints): Interactive statements can be used to stop the simulation when a particular variable, or combination of variables, changes. For example: @(top.cpu1.iunit.ireg) $stop; This code will continue the simulation until the variable changes. However, this statement will not necessarily be the first statement executed after the variable changes. Due to the non-determinacy of Verilog code execution, other statements scheduled to execute at the same time unit may execute before the $stop statement is performed. •Timed simulations: A simulation can be set to run for a certain length of simulation time using a delay and the $stop directive. The following statement suspends and waits for 1000 simulation time units to pass. After 1000 time units, the simulation is stopped. #1000 $stop; |