Test Bench Generation 1: VHDL-Verilog Stimulus |

|

|

|

Test Bench Generation 1: VHDL-Verilog Stimulus |

|

|

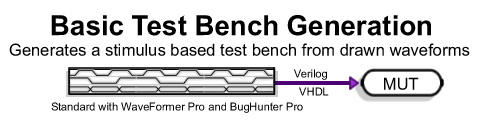

This tutorial describes how to generate Verilog and VHDL basic stimulus test benches using WaveFormer Pro, VeriLogger, Reactive Test Bench Option, and TestBencher Pro. It explores how different waveforms and state values in a timing diagram will affect the generation of the test bench code. It also explores the SynaptiCAD language-independent signal types which allow a single timing diagram to generate both VHDL and Verilog test benches. The generated test benches are normally used with external simulators, and with FPGA tools like Xilinix ISE, Altera Quartus, and Microsemi (Actel) Libero.

SynaptiCAD offers three levels of test bench generation. This tutorial demonstrates the basic level stimulus based test benches that are generated by the default configuration of WaveFormer Pro and BugHunter Pro with VeriLogger. Purchasing the add-on Reactive Test Bench Option allows users to create more advanced self-testing test benches which generate error reports and react to the model under test during simulation. This feature is demonstrated in the tutorial Test Bench Generation 2: Reactive Test Bench Option. The highest level of testbench generation is provided by TestBencher Pro, which allows a user to design bus functional models using multiple timing diagrams and a sequencer process to apply the diagrams. TestBencher can be added to BugHunter or purchased as a standalone product and is demonstrated in the tutorial Test Bench Generation 3: Test Bencher Pro Basic Tutorial.