(TBench) 2.9 Create For-Loop to Perform Multiple Writes and Reads |

|

|

|

(TBench) 2.9 Create For-Loop to Perform Multiple Writes and Reads |

|

|

(TBench) 2.9 Create For-Loop to Perform Multiple Writes and Reads |

|

|

|

(TBench) 2.9 Create For-Loop to Perform Multiple Writes and Reads |

|

|

Loops and nested loops can be placed in the diagram to make the generated test bench apply the same test vectors. Here we will add a FOR loop that surrounds the write and read cycle and applys the waveforms 10 times.

Add the Loop Markers:

•Depress the Marker button so that right-clicks will add Marker lines to the diagram. |

|

•Left-click the positive clock edge at 100ns to select it, then right-click to place the Marker. This attaches the marker to the selected edge. |

|

•Place another marker at the positive clock edge at 800ns by first selecting the edge and then right clicking to add the marker. |

|

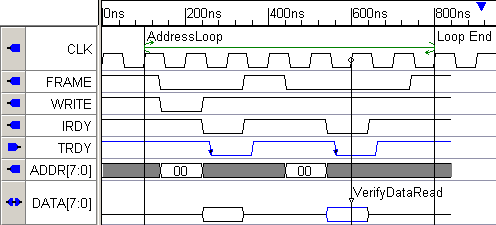

•Double-click on the first Marker to open the Edit Time Marker dialog. •Change the name to AddressLoop, set the type to For Loop, set Index to address, and set end to 10. This will define the variable address that we used in the previous section. •Notice that the marker is attached to CLK 100. If you accidentally attached to the time you can use the controls in that section to attach to the clock. •Then press OK to close the dialog. |

|

•Double-click the second Marker to open the Edit Time Marker dialog. •Set the Type to Loop End. •Set the Display Label to Type so that the marker will display its type rather than its name. •Notice that the marker is attached to CLK 800. If you accidentally attached to a time, you can use the controls in that section to attach to the clock. •Press the OK button to close the dialog. |

|

The two markers should now be connected graphically as shown below. During simulation the diagram between the loop markers will be applied ten times to the model under test. Each time a new value will be read from the file data and written to the model under test because of the @inputData[address]. Then the write will be verified during the read cycle. In this particular case we have written all the values to the same memory location but you could have also parameterized these values or read them in from the data file.

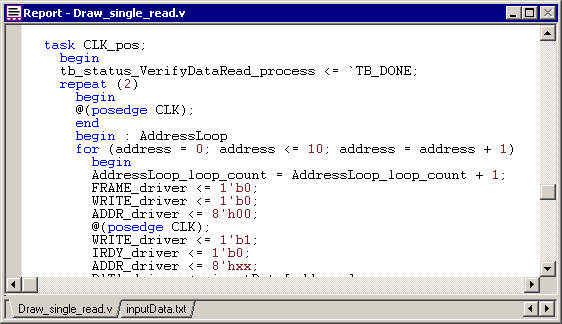

To see the generated code, export the test bench and view the code in the Report tab that contains the generated code. The for loop in the diagram generates a for loop in the generated code.