(Compare) 7: Perform a Clocked Comparison |

|

|

|

(Compare) 7: Perform a Clocked Comparison |

|

|

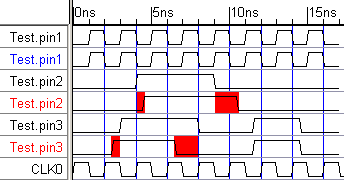

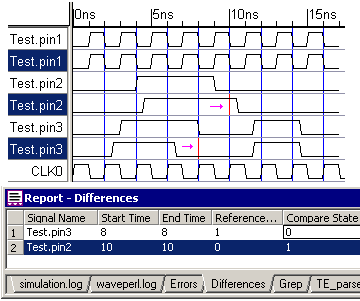

A clocked comparison compares the signal states at clock edges instead of continuously. In this section we will add a clock to the diagram and then set the clock properties of all of the compare signals to reference the clock.

Add a clock signal with grid lines on the positive edges:

•Press the Add Clock button to open the Edit Clock Parameters dialog. |

|

•Set the Period of the clock to 2ns. •Press the OK button to close the dialog and add the clock to the diagram. •Double click on the CLK0 name to open the Signals Properties dialog. |

|

•Press the Grid Lines button to open the Grid Options dialog. We will add a grid to the positive edge of the dialog so that it will be easy to see the sampling points on the diagram. |

|

•Check the Enable Grid box to enable the controls in the dialog. •Enter a Starting Event of 1. This means that the first grid line is drawn on the first event of the clock (in this case it is at 0ns on the positive edge). •Enter an Events Per Line of 2, so that the grid only draws on every-other line. |

|

•Press the Apply button and make sure that the gridlines are on the positive edges of the clock. •Press Ok to close the Grid Options dialog, then press Ok to close the Signal Properties dialog. |

Make the Compare Signals reference the sampling clock:

•Either press the SET ALL button or choose the View > Compare and Merge > Edit Compare Signals menu to select all the compare signals and open the Signal Properties dialog. |

|

•Set the Clock to CLK0 and set the Edge/Level to pos. •Press the Compare button to apply the changes and perform a new comparison. |

|

•Notice that there are now only two differences in the diagram. These two differences occur on the 8ns (on Test.pin3) and 10ns (on Test.pin2) rising edges of the clock. •You can experiment with changing the clocking edge to neg to see how the compare changes. |