(Sim) 1.11 Summary of VeriLogger Basic Verilog Simulation |

|

|

|

(Sim) 1.11 Summary of VeriLogger Basic Verilog Simulation |

|

|

(Sim) 1.11 Summary of VeriLogger Basic Verilog Simulation |

|

|

|

(Sim) 1.11 Summary of VeriLogger Basic Verilog Simulation |

|

|

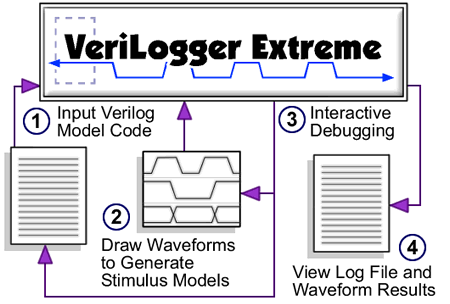

Congratulations, you have completed the VeriLogger Basic Verilog Simulation tutorial. We have demonstrated how to create a project, copy files into the project, simulate and view the results. Chapter 1 of the BugHunter Pro and VeriLogger manual has a step-by-step design flow of how to set up a simulator and create a project. You may wish to read that before attempting a to create a complicated project.

We have also introduced the graphical testbench generation that comes standard with BugHunter Pro. This feature generates a test bench code from a single timing diagram. There are two other levels test bench generation that can be added to BugHunter. The first is the Reactive Test Bench Option that generates self-checking code from the expected waveform information. The highest level is TestBencher Pro which creates bus functional models from multiple timing diagrams and is able to apply randomized data to each transaction.