Test Bench Generation 4: TestBencher Pro with Random Transactions |

|

|

|

Test Bench Generation 4: TestBencher Pro with Random Transactions |

|

|

Test Bench Generation 4: TestBencher Pro with Random Transactions |

|

|

|

Test Bench Generation 4: TestBencher Pro with Random Transactions |

|

|

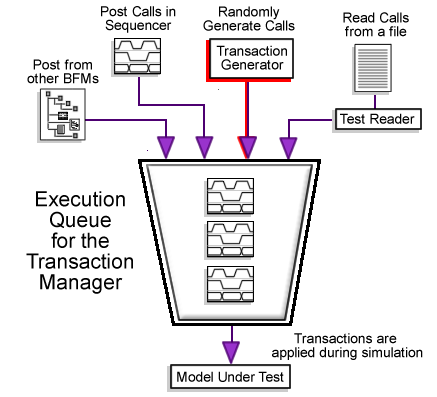

This tutorial demonstrates how to convert a directed-test VHDL test bench project into a constrained-random testbench where transactions are randomly applied to the model under test. TestBencher Pro can generate a Transaction Generator that randomly posts master transaction calls to a Transaction Manager Queue, based on the probabilities specified in a weightings table. A weightings table defines the relative probabilities for the next transaction type based on the type of the most recently posted transaction call. The input data for these randomly selected transactions is automatically randomized using the constraint settings for each input variable when a transaction call is popped from the queue and executed. You will need a license to TestBencher Pro and access to a VHDL simulator to simulate and see the results of this tutorial. These features are not currently supported in Verilog.