Chapter 9: VHDL2Verilog Translation |

|

|

|

Chapter 9: VHDL2Verilog Translation |

|

|

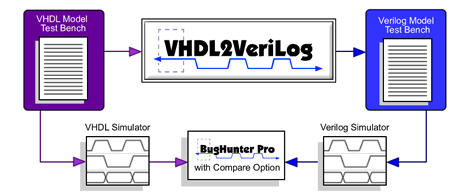

BugHunter Pro can also act as a graphical interface for SynaptiCAD's V2V code translators. To use the features in this chapter you will need a license for VHDL2Verilog in addition to your BugHunter Pro license. The translator can also be run from the command line, but the graphical interface makes it a lot easier to setup the options and see the results.

VHDL2Verilog translates hierarchical IEEE Standard 1076-87 and 93 VHDL to Verilog HDL. It translates all structural VHDL constructs, as well as a large subset of RTL VHDL constructs. Verilog that is created by VHDL2Verilog is functionally equivalent to input VHDL, and because of one-to-one mapping of VHDL to Verilog, is easy to understand. Syntax and semantic checking of the VHDL input is also performed during translation and output Verilog is compatible with any Verilog-XL compatible simulator.

VHDL2Verilog is a valuable design reuse tool because it preserves the level of abstraction during translation. There is a one-to-one mapping of constructs in most cases. Because the abstraction level is preserved, Verilog can remain technology independent in cases where the input is behavioral or RTL.

VHDL2Verilog can:

•be useful to designers working in a VHDL/Verilog environment,

•be integrated into Verilog-only based tools,

•provide library translation (VHDL library => Verilog library) capability, and

•automate the model generation procedure.

VHDL2Verilog can be obtained with an object-oriented Software Procedural Interface (SPI) to access the output HDL, and is currently available on Linux and Windows platform.