9.1 Graphical Interface for Translation |

|

|

|

9.1 Graphical Interface for Translation |

|

|

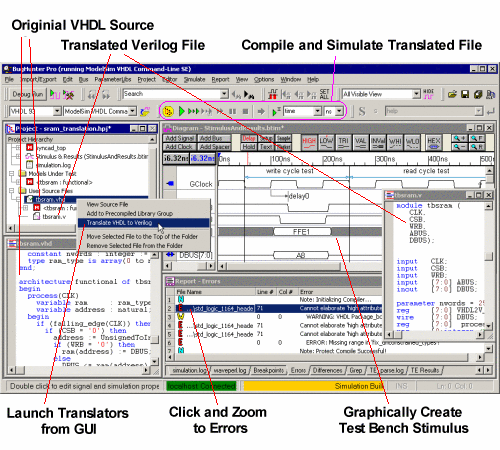

If you have purchased BugHunter Pro or VeriLogger Extreme along with the VHDL2Verilog translator, you can use BugHunter as a graphical interface to the command line translator. BugHunter makes it easy to run the translator, fix errors in both the generated and the original code, verify the translated code with a simulator, and create language-independent test bench code to help test the translated code and compare its functionality against the original code. If you are running VHDL2Verilog from the command line, use the options in Section 9.2: VHDL2Verilog Translation Options to control the translator.

Using BugHunter Pro's Graphical Interface

BugHunter Pro stores the translation options and list of files using a Project file (*.hpj). Before starting a translation, create a project and add in the files to be translated.

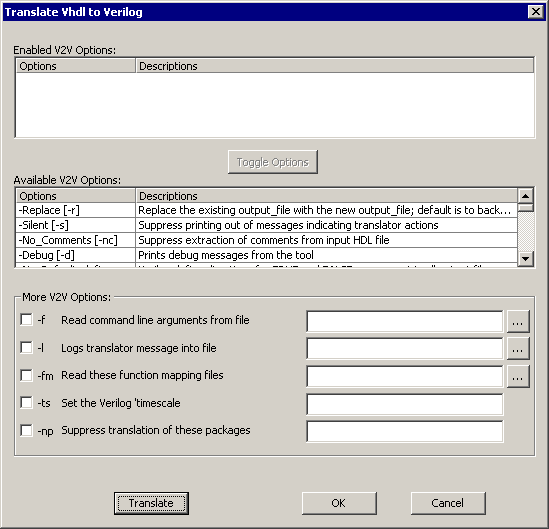

•Open a project or create a new one using the Project > New Project menu option as discussed in Step 3: Create a Project. •Add source code files to the project by right clicking on the User Source Files folder in the Project Window and choosing either Add or Copy Files to Source File Folder menus to open a file dialog as discussed in Step 4: Add Source Files to the Project. •Set the translation options by choosing Project > Translate VHDL to Verilog menu. This opens the translate options dialog. If you press the Translate button in this dialog, all the HDL source files in the project will be translated. |

•VHDL2Verilog provides several options that allow you to tailor the operation of the tool. To enable an option, select it in the Available V2V Options list and then click the Toggle Options button in the middle to move it to the Enabled V2V Options list at the top of the screen. |

•To translate a single source file in your project, right click on one of the source files and choose a Translate function from the context menu. The options set in the previous step will be used to translate the file. We generally recommend translating one file at a time. |

|

•The translated file will appear underneath the original file. Double click on either file to view the source code it contains. |

|

Fix errors in the original model code:

Once a new file is generated, there may be translation errors because the mapping between languages is not a perfect match. Errors found in the generation file will be listed in the simulation log tab of the Report window. Double clicking on an error will open the original code in an editor window so that you can quickly work through those errors.

When there is a decision that the translator could not resolve, the translator will often leave some placeholder code in the generated code. The intention of the placeholder code is to create a compile error if you try to simulate the translated code before fixing the problem and to also give you a hint as to what needs to be added at that particular point.

Below is an example where the translator could not find the definition for the 'high attribute so it inserted some placeholder code and reported an error.

Original VHDL code

subtype natural is integer range 0 to integer'high;

variable address : natural;

Translated Verilog with Placeholder error “integer /* ignored attribute: 'high */”

reg [0:integer /* ignored attribute: 'high */] process_1_address;

The solution here would be to select the desired bit size for your Verilog representation of the address signal and manually modify the generated code. For example:

reg [0:15] process_1_address;

Verify the translation with a simulator

BugHunter can also act as a graphical debugger for your own simulators. First you will need to set up BugHunter to work with your simulators by using the Options > Simulator / Compiler Settings to open a dialog and fill out the simulator information. See Chapter 1: Getting Started with BugHunter for information on setting up an external simulator.

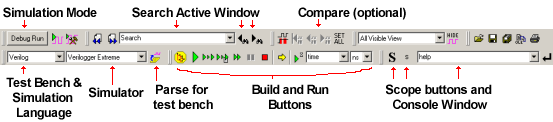

It is frequently useful to create two compile configurations for your BugHunter project (one for compiling the original source code and one for the translated source code). You can set the Compile Source Files Of Type check boxes in the General tab of the Project Simulation Properties dialog so that one configuration only compiles Verilog files and the other configuration only compiles VHDL files (See Section 2.1 Project Simulation Properties).

Next, you can simulate using the Build and Run buttons. The compiler that runs will be determined by the settings in the Test Bench Language and Simulator dropdown boxes on the main button bar. See Chapter 2: Simulation and Debugging Functions for more information.

Create language-independent test bench code

BugHunter Pro can also take simulation results from one language and create a testbench with the other language. See Chapter 3: Waveforms and Test Bench Generation for more information on drawing and managing test benches.