(TBench) 1.5 Exporting to VHDL |

|

|

|

(TBench) 1.5 Exporting to VHDL |

|

|

Next we will export to a VHDL test bench. If you are a Verilog only person, you can generate a Verilog test bench instead and investigate how the integer signal got exported to Verilog.

Generate the VHDL Test Bench:

•Choose the Export > Export Timing Diagram As menu option to open the Export dialog. |

|

•In the Save as Type list box in the lower left corner of the dialog, choose the VHDL (*.vhd) script. This indicates that the timing diagram will be exported to a VHDL code file with a default file extension of ".vhd". |

|

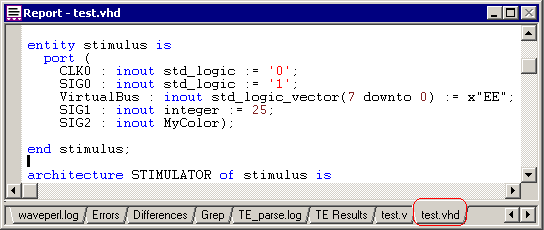

•Choose test.vhd as the file name and click the Save button to close the dialog. WaveFormer Pro will produce a VHDL file named test.vhd. •The file test.vhd is automatically displayed in the Report window. If you cannot see the Report window, select the Window > Report Window menu option to bring the window to the top. |

Compare the Code to the Diagram:

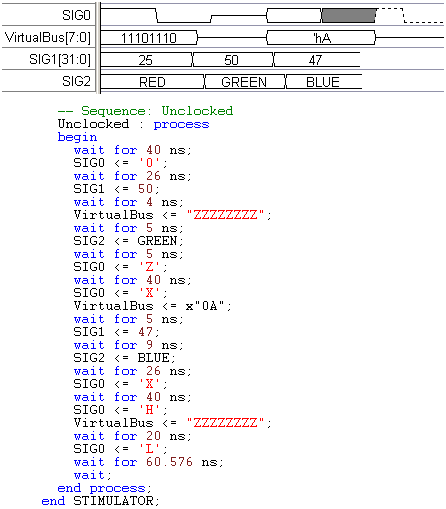

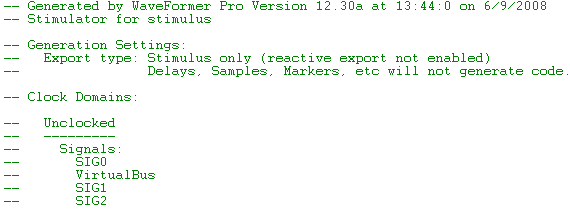

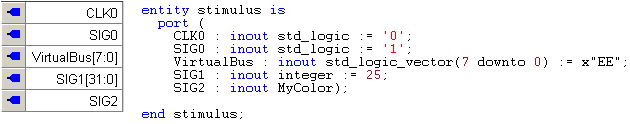

View the file test.vhd inside the Report window. Notice the entity and architecture structures and the types of all the signals. CLK0 uses a while loop to calculate its value. SIG0 shows how the graphical states are exported. VirtualBus is defined as an 8-bit logic vector. SIG1's values are exported as integers. SIG2's values are exported as RED, GREEN, and BLUE.

•At the top of the file there is a large comment section that describes how the code was generated, what the clocking domains are, and what program features were used to generated the code. In the basic testbench generation, all signals are in the Unclocked domain (all signals are delayed by time values). With the reactive test bench option, you can delay signals based on the occurrence of clock edges as well. |

•Notice that each of the output signals in the diagram are also inout of the stimulus entity. These signals will hook up to your model under test. |

•CLK0 is defined as a clock signal in the timing diagram. The program generates a loop to represent the clock (rather than a series of assignment statements for each edge). Also notice that all of the clock properties such as buffer delay and rise and fall jitter will generate proper code. |

|

•Compare the signal waveforms to the generated code. Notice that the undefined valid state on SIG0 generates to 1'bx, but the defined valid states on Virtual bus generate out to the proper values. |