(TBench) 2.7 Add a Sample to Verify Data Read from MUT |

|

|

|

(TBench) 2.7 Add a Sample to Verify Data Read from MUT |

|

|

(TBench) 2.7 Add a Sample to Verify Data Read from MUT |

|

|

|

(TBench) 2.7 Add a Sample to Verify Data Read from MUT |

|

|

Samples can be used to verify data that is generated by the model under test during simulation. Here we will add a Sample to the Data bus to verify that the read cycle worked correctly.

Add a Sample to verify the read cycle:

•Press the Sample button so that right clicks will add delays. |

|

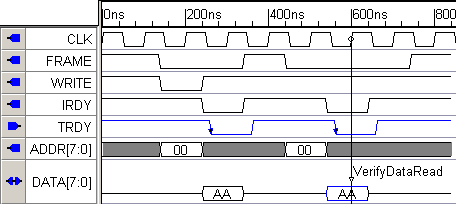

•Left-click on the positive CLK edge at 600ns, then right-click on the DATA segment directly below it (slightly to the right). This will place a Sample that will trigger at that clock edge and verify that the data read from the MUT is what we expect (indicated by the waveform drawn under the Sample). |

|

•Double-click on the Sample name to open the Sample Properties dialog. •Change the sample name to VerifyDataRead •Press the HDL Code button to open the Code Generation Options dialog. |

|

•The If condition should be set to Sample State Matches, which is the default behavior for a sample. •Set the Then Action, to Display Message so that each time the sample passes it will generate a log messages stating that it passed. And give it a warning level of Note. •The Else Action should be set to Display Message so that each time the sample fails it will generate a log message stating the error. •Press OK to close both dialogs. |

|

Here is what the diagram should look like after adding the Sample:

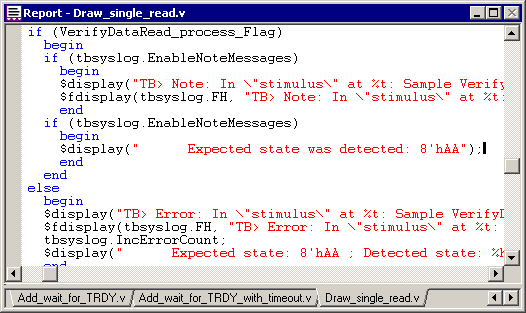

To see the generated code, export the test bench and view the code in the Report tab that contains the generated code. Locate the CLK_pos sequence, then search down for VerifyDataRead to see the code generated for the sample.