(TBench) 2.10 Alternate Test Bench Designs |

|

|

|

(TBench) 2.10 Alternate Test Bench Designs |

|

|

The test bench for this tutorial has been a very simple one-loop read and write cycle. However with very small changes you can control the order of the reads and writes and also write random data instead of the data from the file. We will not perform these steps but you can look at the diagrams and see how it is done.

Alternalte: Consecutive Writes followed by Consecutive Reads

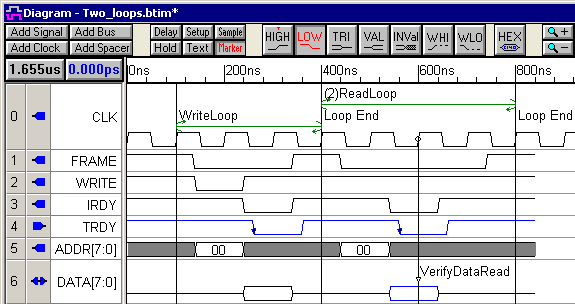

If you want to perform multiple writes concurrently, followed by multiple concurrent reads, then two for-loops are needed. The array of data can be referenced in each loop in the same manner already demonstrated. The (2) beside the ReadLoop label shows that it was added after the LoopEnd marker.

Random Data instead of the File data

In Verilog, you could use $random() as the state value for DATA during the write transaction. A user-defined function can also be embedded into the generated test bench using the Class Methods dialog which could be used to generate data values. In both of these cases, you would need to modify the state value under the VerifyDataRead sample since the inputData array is no longer used. A Sample must be placed on the driven DATA segment to capture the expected data. For example, you could create a Sample named ExpectedData that is triggered from the clock edge at 300ns. Then the state under the VerifyDataRead Sample would be set to ExpectedData instead of @inputData[address].