(TD) 6.5 Incremental Simulation |

|

|

|

(TD) 6.5 Incremental Simulation |

|

|

One common problem in simulating and debugging digital systems is that large parts of the design have to be entered before testing can begin because the parts provide input to each other. One solution is to break a design up into pieces and test each piece with test vectors that represent the output of the other pieces. However, generation of the test vectors can be time consuming.

SynaptiCAD products provide a very simple and quick method for testing small parts of a design: graphically draw the signals for the missing parts of the design to test the design at its current state of development. Then later add the design information that models these signals (in other words, we temporarily model simulated outputs as drawn inputs).

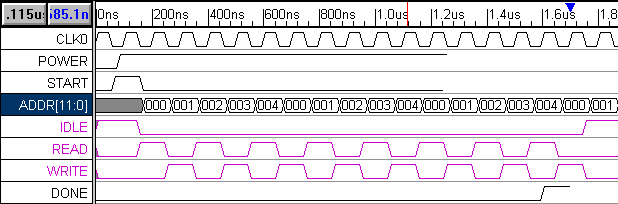

We will now use this method below to verify the operation of our state machine before we enter the HDL code that generates the DONE signal:

1. Add a signal called DONE.

2. Draw a low segment for 1.6 us, followed by high pulse that lasts for at least one clock cycle. Click on Apply to run the simulation.

3. The diagram should now show the simulation output from your state machine. The simulated signals are pink to distinguish them from graphically drawn signals.

Make sure everything is working properly:

1. First make sure that the simulation status indicators read ![]() Simulation Good. If the indicators still show an error, then the simulation.log file will help you to pinpoint the error in your diagram.

Simulation Good. If the indicators still show an error, then the simulation.log file will help you to pinpoint the error in your diagram.

2. Next, check your diagram against the figure above to verify that your state machine is simulating correctly.

3. If the simulation succeeded and there are still discrepancies in the output, check your design equations and the input stimulus you’ve drawn (START and DONE signals).

Once you have the circuit simulating properly, let’s see what happens if the START pulse gets too small:

1. Drag the falling edge of the START pulse back to approximate 140 ns (before the falling clock edge at 150 ns). This step causes the state machine to stay in the IDLE state (the IDLE signal stays high).

2. Double click on the falling START edge and enter a time of 160 into the Edge Properties dialog to restore proper operation.