3.1 Virtual Buses |

|

|

|

3.1 Virtual Buses |

|

|

A Virtual bus is a signal that is defined as having multiple bits and generally drawn using valid, invalid, and tristate waveforms. A Virtual bus will export to VHDL and Verilog as a multi-bit signal. This is the most common type of bus and is the easiest to draw and work with.

Create a virtual bus:

•Fastest method: Make sure no signals are selected, then click the Add Bus button to open the Add Bus dialog. Then select the Virtual Bus radio and set the MSB and LSB values. •Alternate method: Add a signal and then double-click on the name to open the Signal Properties dialog. In the dialog edit the edit the MSB and LSB values. |

|

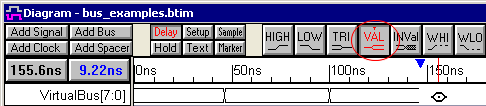

Draw Virtual Bus Waveform Segments:

•Sketch the bus waveform using any of the waveform states. To quickly draw consecutive valid states click twice on the Valid state button (or double click on it) so that it is red and also has the red T on the top of the button. This will stop the button from toggling. |

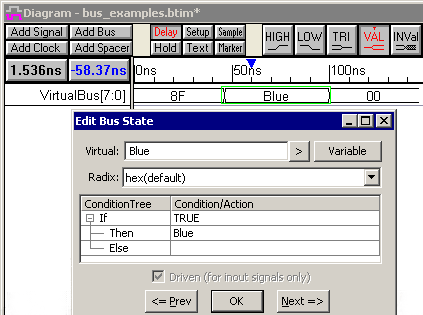

Define the Values of the Waveform Segments:

•Open the Edit Bus State dialog by either double-clicking on a segment OR first selecting a segment and then clicking the HEX button on the button bar. |

•In the Virtual field, type in the segment value. This can by any type of data including text with spaces (e.g., A0C, 5 + 3, blue level, and 24 are all valid virtual states). •Use Next and Prev buttons, or the <Alt>-N and <Alt>-P keys, to move between the different segments on the same bus. |

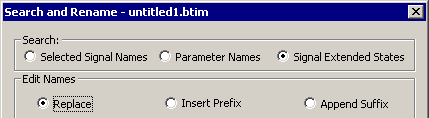

Search and Rename Bus State Values

•Choose the Edit > Search and Rename menu to open a dialog. |

•Select Signal Extended States and the fill the rest of the fields with regular expressions that will match to a state value. See section 11.1 Signal Names for export and import for examples of the regular expressions that can be used in the dialog. |

Bit-Slicing Virtual Buses

•To display a bit-slice of a virtual bus, use the Waveform Library feature described in Section 1.8 Referencing Waveforms from Libraries. •To display a bit-slice of a simulated (watched) signal, you don't need to use the waveform library feature (although it will also work), just change the MSB/LSB of the signal or a copy of the signal as shown in Section 3.4: Bit Slicing a Watched Signal of the BugHunter and VeriLogger manual. |