(SDC) 3: Enter Derived Clocks |

|

|

|

(SDC) 3: Enter Derived Clocks |

|

|

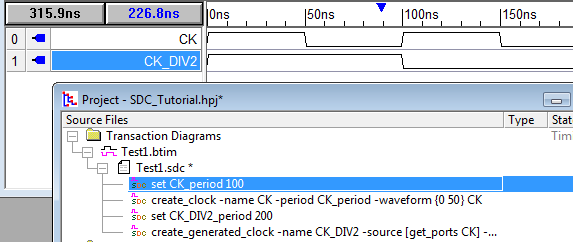

To properly represent the relationship between the master clock and the "divide by 2 clock", we will create a derived clock with the CK clock acting as a reference clock and specify a divisor of 2. Derived clocks produce created_generated_clock SDC commands, unlike regular clocks which produce create_clock SDC commands.

•Press the Add Clock button and create a clock called CK_DIV2. •Choose CK as the Reference Clk to link the two clocks together. •In the Divisor Value box, type 2 to make this clock a divide by 2 of the master clock. •Also, change the Pulse Width to 2 to make the the derived clock to be high for half the time of the master clock (gives clock a 50/50 duty cycle). •Press the SDC Code button at the bottom of the dialog to open the Clock Synopsys Design Constraint dialog. |

|

•As before, check the Create Clock Period Variable check box to create an SDC variable called CK_DIV2_period, and choose Default Clock from the Clock Type drop-down box to generate an SDC create_generated_clock command that uses this variable. Close the two dialogs. •You can see the newly generated code in both the Report and the Project windows. |