|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

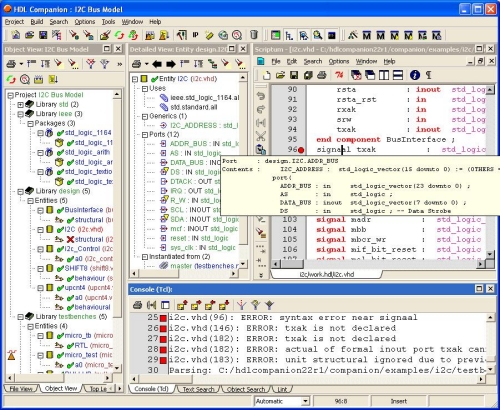

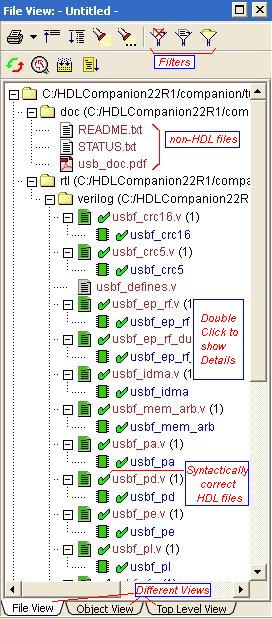

HDL Companion for design explorationHDL Companion helps you explore any HDL design, including third party IP, legacy code and other HDL sources. HDL Companion scans design directories and uses the information to generate a hierarchal view of the HDL code and all supporting files. The embedded fuzzy parsers accept any Verilog, VHDL or mixed HDL design code; even if the code is incomplete or contains errors. Syntactically correct HDL can also be linted to find problems not reported by the compilers. The GUI offers many ways to navigate through the design and explore the details you're looking for including a tree browser, hierarchial chart, signal trace charts, text editors, and lint results. The GUI can also launch your simulator. HDL Companion is an excellent tool for navigating through a design and it is especially useful for investigating designs that are unfamiliar.

Global Views

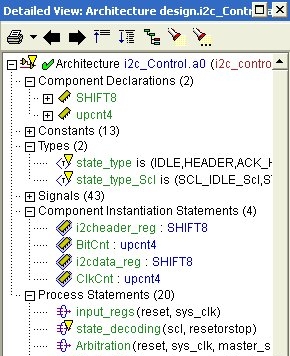

Detail View Window

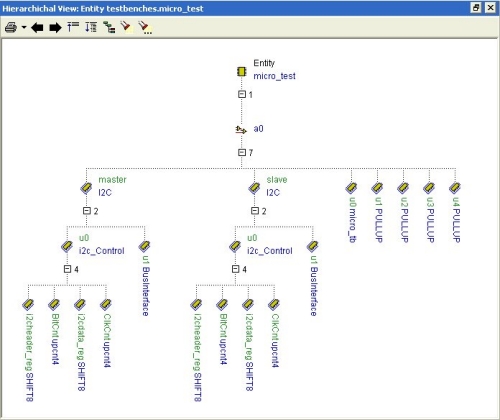

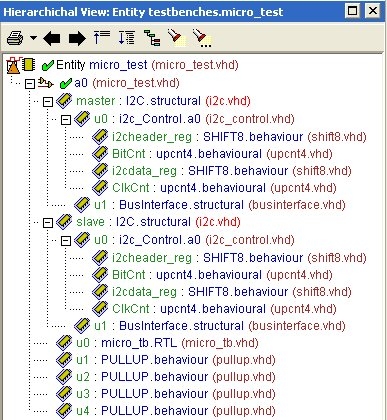

Hierarchical ViewYou can create a hierarchical overview for each entity/module in your project. The hierarchy can be displayed in 2 modes. One is tree view mode, also used in the other views. The other is the graphical mode, which resembles the traditional top-down view. Below is an example of the hierarchy for an I2C model with testbench displayed in the 2 modes.

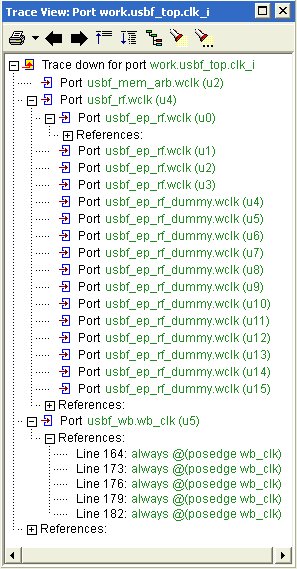

Trace View

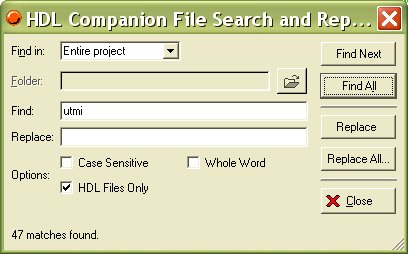

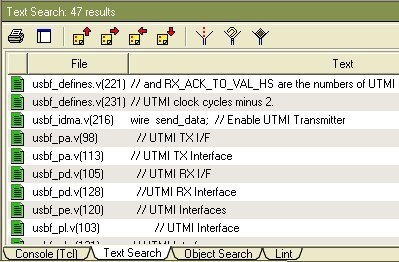

Search and Replace

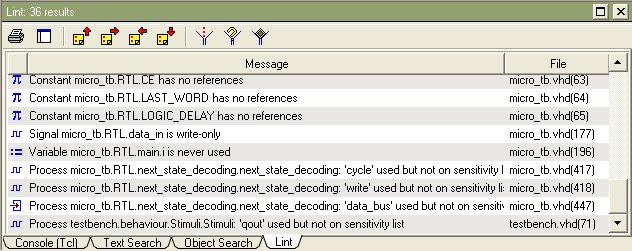

Linting your DesignThe lint tool analyzes your VHDL or Verilog code and reports potential problems which are not found by the compilers. It offers you a simple but fast method to improve the quality of the HDL code. It is intended to find all kinds of language constructs that are formally correct but probably not intended. Examples are signals that are defined but never used; signals that are on the sensitivity list of a process but not used inside the process; etc. You can run the Lint tool on the whole project or on packages, entities or modules separately. The results are displayed in the Lint tab of the Console Window. You can double click on a message to jump to the source file and inspect the HDL code.

HTML Document Generation from VHDL and Verilog source codeHDL Companion comes with an integrated HTML generator that allows you to export your project in a format that is easily accessible to others. VHDL and Verilog files will be translated to HTML including hyperlinks that allow easy navigation from identifiers to their definition. To make the code more readable, color coding is used to highlight the VHDL and Verilog keywords. The generated HTML also includes an index (both alphabetical and by type), an object view, a file view and a hierarchical view. Detailed information for high level objects (packages, entities, architectures, configurations and modules) is also available. All objects shown in the different views contain links that allow you to quickly navigate through the differents views and the HDL files. The generator simplifies the way you communicate your design to others. The hot links and color coded HDL files shorten the time needed to understand the design. NEEDS Link to HTML Project EDA Tools ConfigurationThe support for other EDA tools has been split in two parts. The philosophy behind this approach is that you define your available tools (and different versions of them) once; and select which versions to use per project. This also allows you to easily switch between vendor and tools versions during your project. Second advantage is that HDL Companion will add these tools to your program path and set the required environment variables. The EDA Tools Selection wizard allows you to select the appropriate tools and set the options for these tools. Extra tool buttons will be added to the GUI for easy access to the selected tools. A list of tools supported by default is provided below. Other tools or vendors are easily added through the Tcl interface. Simulation tools:

Synthesis tools:

The FPGA Vendor tools from:

Click here to download EASE, HDL Companion, or IO Checker The interface to the third party tools is via Tcl scripts. This makes it very easy to add other third party tools to meet your needs. |

||||||||

|

|