|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

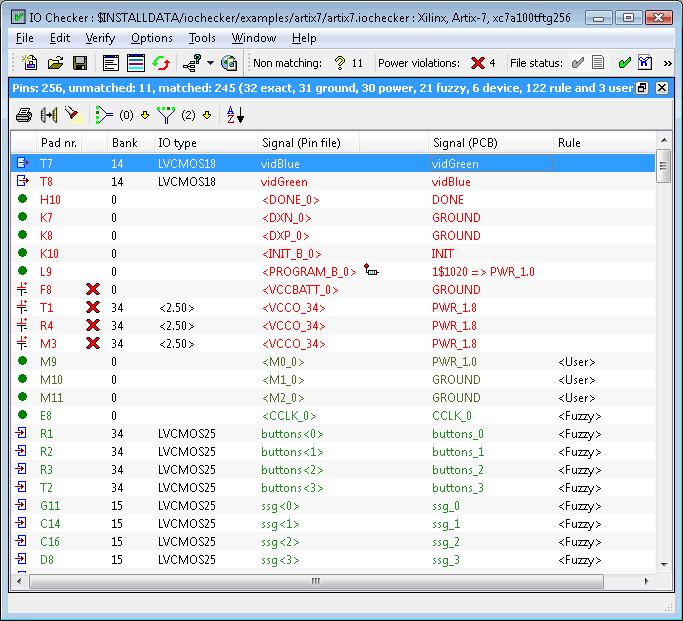

Press Release for Product Upgrade: March 15, 2013 SynaptiCAD presents IO Checker 2.2, the FPGA and PCB IO verification toolSynaptiCAD now has new versions of HDL Work's IO Checker that will verify that signal names used in the FPGA are connected to the appropriate signals on the PCB. Additionally it verifies the voltage values connected to the FPGA power and reference pins. IO Checker uses rules (based on regular expressions) to match the signals names in both the FPGA and PCB design environment. The rules can be generated automatically and be fine-tuned by the designer. This automated approach will often match 80% to 90% of all device pins.

The flexibility of IO Checker allows it to be used in any design flow and does not require any design methodology. The rules generator in combination with the sorted "problem view" allows engineers to validate a 1000+ pins device in about 30 minutes. New functionality in IO Checker 2.2:

Pricing and AvailabilityIO Checker pricing varies between $945 and $6615 based on the number of FPGA vendors supported and the pin limit. IO Checker can be downloaded from SynaptiCAD's website www.syncad.com. An automated web license utility can be used to get a temporary evaluation license. Marketing ContactFor any questions concerning this press release please contact Donna Mitchell at 540-953-3390 or email at [email protected]. |

|

|