|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

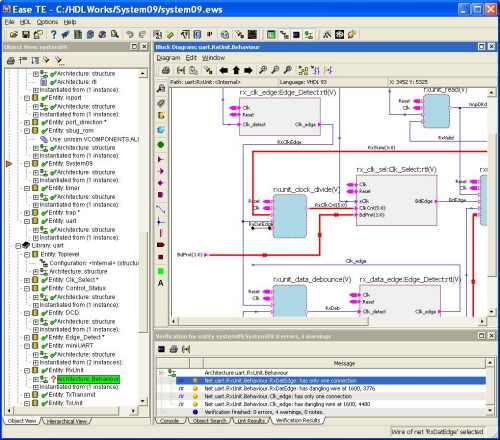

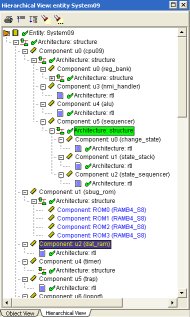

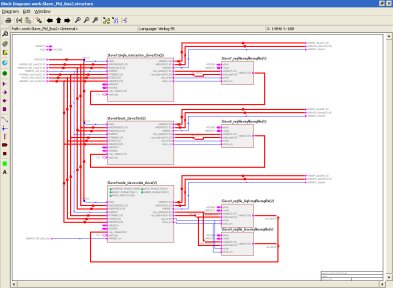

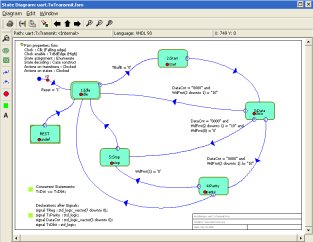

EASE Block and State Diagram HDL EntryEASE offers the best of both worlds with your choice of graphical or text-based HDL entry. You don�t need to be a master of either Verilog or VHDL. When you're creating a new design, just enter your design using your preferred mix of graphics and text. EASE automatically generates optimized HDL code for you in the selected language - VHDL or Verilog. EASE supports industry standard version control environments that deal with design and configuration management, enabling multiple users to work simultaneously on one EASE project.

Features & Benefits

Project browser

Block Diagram Editor

State Diagram Editor

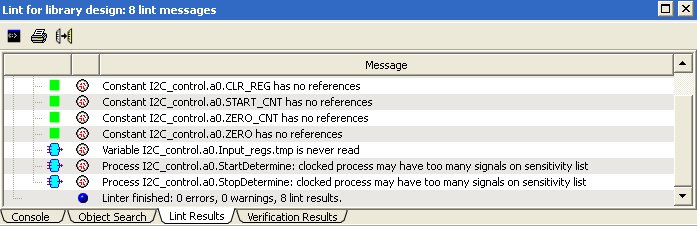

Truth Table Editor

Integrating external HDLExternal HDL files like IP, legacy code, Matlab code and FPGA generated models can be integrated in your project as external objects. EASE will create symbols and component declarations for instantiated modules. Symbols can be easily updated to the latest version of your code. Existing HDL can also be translated into block diagrams. Symbol libraries for FPGA primitives can be created on the fly from vendor VHDL or Verilog descriptions. Verification and LintingBefore VHDL or Verilog is generated, EASE verifies the design for inconsistencies and syntax errors. Linting is an additional verification effort that identifies potential design problems (like range mismatches in assignments of vectors, or read-only signals) and optimizes the design by identifying unused signals and definitions. Errors, warnings and notes are reported in the verification pane. The messages are hot-linked to the corresponding editor to quickly navigate to the offending code.

Team based designMany FPGA's and ASIC's are designed by a team of engineers that need to work closely together to finish the implementation successfully and on time. The best way to work together on a project is by using a design environment that allows a group of designers to simultaneously work on the project without interfering with each other. EASE supports team-based design using industry standard version management systems like RCS, CVS, ClearCase and Subversion. All designers in the team can check-in/check-out objects at the entity/module level. This fine grain control allows you to edit the parts that you need to work on while your colleagues can still read these parts. 3rd Party InterfacingEASE has a user configurable third party tool flow interface. A wizard will help the user to select the appropriate tools and set the options for these tools. Extra tool buttons will be added to the GUI for easy access to the selected tools. A list of tools supported by default is provided below. Other tools or vendors are easily added through the Tcl interface. Simulation tools:

Synthesis tools:

The FPGA Vendor tools from:

HTML GeneratorThe HTML Generator generator allows you to export the whole project on your intranet or to the internet. With a single click, EASE will export all diagrams, side data, generated HDL code and the project structure to the desired location in HTML and SVG files. SVG (Scalable Vector Graphics) is the W3C standard XML-based imaging model started by Adobe. Graphics created in SVG can be scaled without loss of quality across various platforms and devices. The exported HTML contains hot links in the diagrams and the project structure to easily navigate through your design. Standards SupportEASE's code generator produces HDL output conforming to IEEE-1076-87 and IEEE-1076-93 VHDL standards, as well as the IEEE-1364 Verilog standard. EASE also supports the industry's leading simulators and synthesis tools, as well as version control features when provided. Supported PlatformsHardware Platforms & Operating Systems

System Requirements

License Configurations

Click here to download EASE, HDL Companion, or IO Checker Would you like a quick walk-through of Ease? Download the evaluation version, call 540-953-3390 and ask for Gary. He will give you a brief tour which covers important areas like: block diagram editing, state machine and truth table editing. |

||||||||

|

|