|

Version 12.0 Features

SynaptiCAD is proud to release version 12.0 of GigaWaveViewer, Timing Diagrammer Pro, WaveFormer Pro,

DataSheet Pro, BugHunter Pro, VeriLogger Pro, and TestBencher Pro. Below are some of the new features:

New Timing Diagram Editing Features

- Updated and improved online help that is compatible with Microsoft Vista security requirements.

Includes more images and better organization.

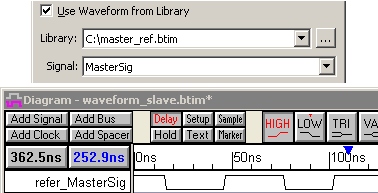

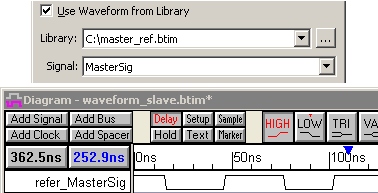

- New waveform libraries allow a signal to be defined by a reference waveform in a waveform

library.

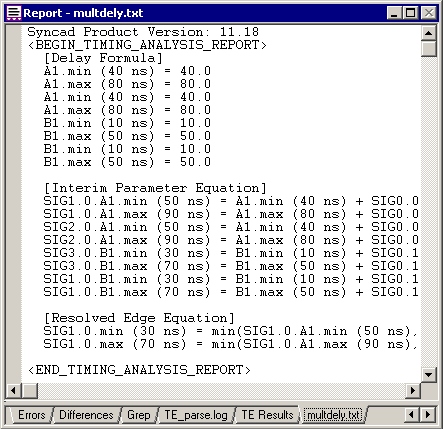

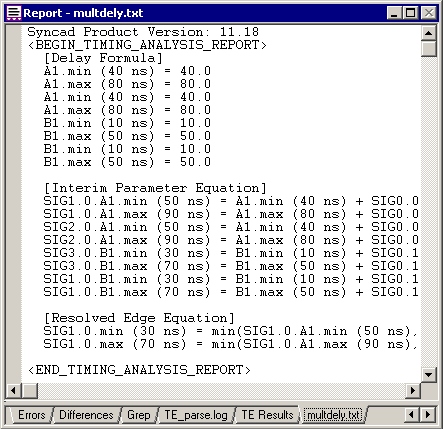

- New Timing Analysis Reports show how all the timing calculations were made.

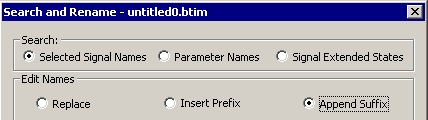

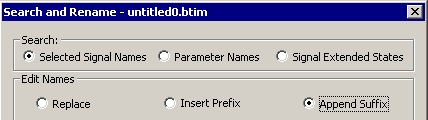

- Search and Rename function now supports replacing parameter names and bus values in addition

to signal names. Adding prefixes and suffixes to names is also supported.

- Search control searches in currently active window. Supports searching for signal names

in the diagram window, parameter names in the parameter table window, HDL source in the editor windows,

strings in the report window tabs, and strings in the project tree window.

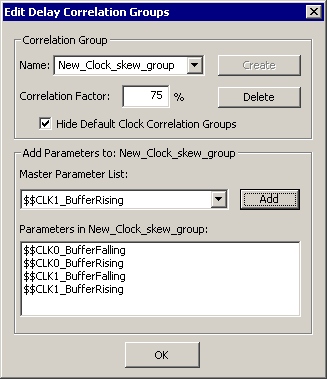

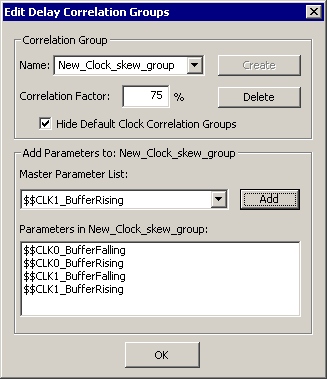

- Buffer delays from clocks derived from other clocks can now be correlated. See Section

2.4 Modeling Clock Skew with Delay Correlation.

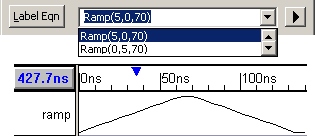

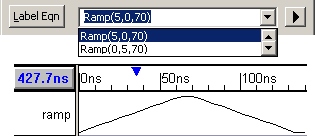

- Added new ramp functions for generating analog signals using label equations.

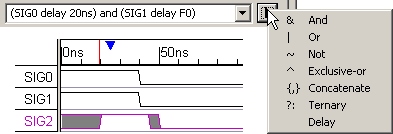

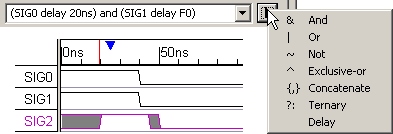

- New "quick fill" buttons make it easier to write valid equations. Lookup buttons added

for Boolean equations and Label equations.

- New printing feature, scale to screen, allows fonts in diagram window to shrink to create

more accurate WYSIWYG images when printing the diagram based on the time range shown on the screen.

- Edge placement dialog now displays state for single bit signals as well as for buses.

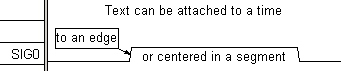

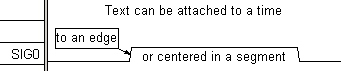

- Text attached to edges can optionally be drawn with a bubble around the text and a line

drawn to the edge. This is set using the show connection check box in Edit Text dialog.

- Use the thickness control to set width of grid lines on clocks and signals.

- Faster timing analysis for very large timing diagrams.

WaveFormer Pro and TestBencher Pro Features

- Much faster VHDL and Verilog test bench generation.

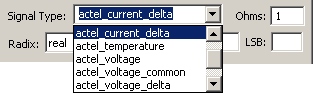

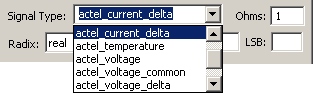

- Added support for Actel Fusion analog data types.

- Expandable Verilog and VHDL editor for simulated signals.

BugHunter Pro

- New buttons for navigating backwards and forwards through most recently visited locations

in HDL source files.

- Updated to support latest versions of 3rd party simulators.

- GUI support for signal and expression breakpoints that trigger based on value changes

on nets and registers.

- New controls to support "Run for Time" functionality

VeriLogger Extreme

- Support for switch primitives (nmos, pmos, tran, tranif0, etc) including support for

strengths.

- Increased speed when performing VCD dumps.

- Improved error reporting and syntax checking.

- Support for signal and expression breakpoints

- Miscellaneous speedups in compile and simulation time

- Full support for generate statement

- Increased parser speed

- Support for $plusargs functions

- Reduced memory usage of simulation runtime

WaveViewer and GigaWaveViewer

- Faster conversion of bits to virtual buses. This can speed up loading of VCD files by

as much as 10 times!

- Faster rendering of group buses.

- Convert bits to group buses or virtual buses.

New Features pages for previous versions:

List of Features in Version 11.0

List of Features in Version 10.0

|