|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

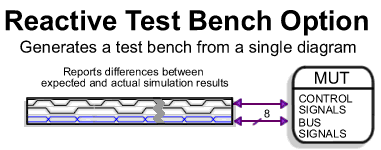

Reactive Test Bench Generation OptionThe Reactive Test Bench Generation Option bridges the gap between the stimulus waveform test benches that are native to most of the SynaptiCAD product line and the bus-functional model generation of TestBencher Pro. This option allows users to describe single timing diagram test benches that react to the model under test and generate pass/fail reports. The Reactive Test Bench Generation Option can be added to WaveFormer Pro, WaveFormer Lite, DataSheet Pro, VeriLogger Pro, and BugHunter Pro.

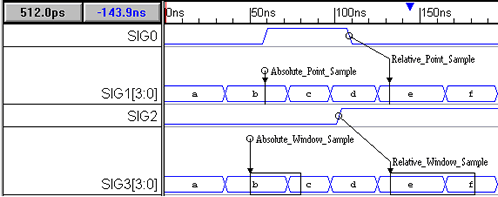

Reactive Simulation ChecksWith "Reactive Test Bench Generation", users have the option of drawing "expected" waveforms on the MUT output ports and adding "samples" to the waveforms to test for specific cases. During simulation, the code generated by the samples would watch the output from the model under test and compare it to drawn states. Samples can perform a variety of functions such as pausing the simulation to debug a problem, reporting errors and warnings, user-defined actions, and triggering other samples.

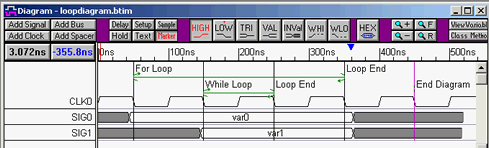

Reactive Loops Conditional Apply StimulusThe Reactive Test Bench Generation also includes markers that can be used to wait for activity from the model under test and/or loop over a section of a diagram. Markers can also be used to call user-written HDL functions ands tasks from within a diagram.

Clocked and Time Based Test Bench GenerationReactive test bench generation also allows the option of creating "clock-based" test benches as well as the "time-based" test benches currently supported by the stimulus based generation models. Clock-based test benches delay in clock cycles instead of times, allowing the user to change his clock frequency without needing to change his timing diagram. Clock-based test benches are also required when testing using high-speed "cycle-based" simulators.

|