|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

TestBencher VHDL, Verilog, and TestBuilder Support

TestBencher Pro provides designers with a graphical environment for rapidly generating system level

test benches composed of cycle-based or time-based bus functional models. TestBencher Pro's graphical

interface speeds up test bench development for both expert and novice users. TestBencher generates all

of the low-level transaction code, verification code, sequence detection, error reporting and file I/O

code. The graphical representation also enhances the ability of engineers to share data across projects,

even for new engineers not yet familiar with the details of the test bench design.

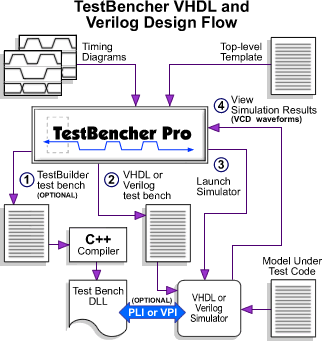

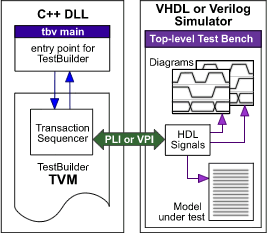

TestBencher Pro VHDL and Verilog Design FlowTestBencher Pro generates VHDL and Verilog test benches directly from timing diagrams. The test benches use a bus-functional model architecture that enables test bench models to be created from data contained in component data sheets. The generated test benches can be compiled and simulated using all major VHDL and Verilog simulators. If TestBuilder library support is enabled, the user's C++ source files are automatically compiled by TestBencher using either GNU gcc or Microsoft's C++ compilers. TestBencher controls the compiler and simulators so that the test bench is seamlessly built and linked into the simulator transparently each time the user updates his test bench source files. All waveform results and log files from a simulation run are automatically imported and displayed inside TestBencher so that you develop and test your design without needing to leave the TestBencher Pro graphical environment. System Level DesignTestBencher Pro generates the entire test bench using graphical timing diagrams, information extracted from the model under test, and a top-level test bench file. The only code that the user writes is at the system level, all of the other code is automatically generated. In the sequencer process of the top-level test bench file, the user specifies the order and logic for applying the timing diagram transaction procedure calls to the model under test by selecting from a list of available transactions. TestBencher C++ Library SupportTestBencher supports C++ integration using the open source TestBuilder libraries from Cadence. This allows TestBencher to generate VHDL and Verilog test benches that have access to power features like random data generation and temporal assertions that are not built into the standard HDL languages. TestBencher generates all of the TestBuilder code and the interface code between the C++ libraries and the simulator. TestBencher also handles all of the external compiler and simulator control necessary to build the C++ dynamic libraries, link them to your HDL simulator, and run the simulation.

Verifying Data with SamplesTestBencher Pro generates state and timing protocol checkers for verifying the response of the model being tested. Protocol requirements are specified using TestBencher's graphical sample construct. Samples are placed on signals in the timing diagram and normally monitor signal values coming back from the model under test. Depending on how they are drawn, samples can monitor a number of different events such as:

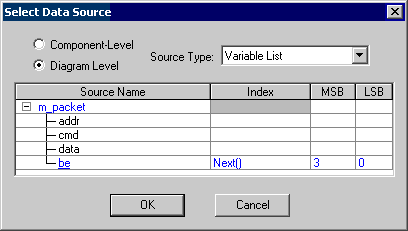

Sample window intervals can be specified as an amount of time or number of clock cycles (to support cycle-based test bench generation). The sampled data can be stored and used in various types of data targets, used later in the same transaction, other transactions, passed up to the top-level test bench, or saved to a file. Samples can also be linked to other samples and delays to verify more sophisticated protocol requirements. Samples have many pre-defined actions that can be performed based on whether the sample passes or fails. The default action is to display an error message if the sample fails. Some of the other actions supported are: ending the current transaction, restarting the transaction, breaking to a debugger, driving a signal state value at a specified future time, and conditionally triggering other samples. TestBencher also has the capability of creating user-defined conditions and actions for samples, so users can customize sample actions to perform application-specific functions that they commonly want to use in their test benches. Constrained-Random Data StructuresTestBencher Pro provides the capability of easily creating complex data structures that can be used to supply or store state information. These data structures allow the user to easily read data from and write data to table-formatted files, queues, arrays, and associative arrays. Data structures are particularly useful for modeling packet-based protocols (for example, to test devices on an I/O channel) since data structures enable grouping of packet information into discrete units. Data structure packets can be passed as parameters to transaction function calls, defined local to a transaction, or defined globally for access by all the transactions in a bus functional model.

Automatic Updating of Signal and Port CodeOne common annoyance when working with HDL languages is maintaining the signal and port information between the test bench and the model under test. Signal information is repeated at several levels of the test bench so that a change in the signal information requires changing code scattered throughout the test bench. TestBencher solves this problem by maintaining signal and port information for all the timing transactions and the model under test. Without this capability, port connection errors can easily arise, leading to subtle, difficult to debug errors, similar to the problems that arise when pins are mis-connected on a circuit board. Reporting and Logging FacilitiesTestBencher provides detailed log information during simulation. The log file reports the starting and ending times of each transaction and the success and failure of protocol checks within a transaction. Each type of protocol check also provides a verbosity setting that allows this information to be turned off for all elements of that type. SummaryTestBencher Pro delivers a consistent and efficient solution to the most demanding verification problems. Using TestBencher to generate VHDL and Verilog test benches allows verification engineers concentrate on the verification of the device under test and not on the implementation of the test bench. |

|

|