|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

SynaptiCAD bridges the gap between Agilent's Logic Analyzer/Pattern Generator and Simulation Environments

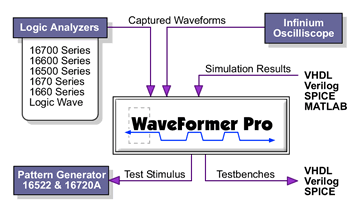

WaveFormer Pro translates Agilent and HP Logic Analyzer data into stimulus vectors for VHDL, Verilog, SPICE, ABEL, Agilent Pattern Generators, and HP Pattern Generators.

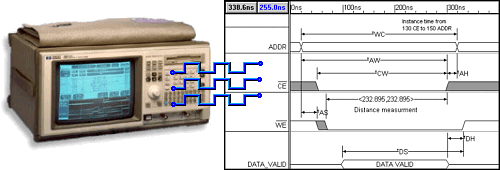

WaveFormer Pro is the perfect companion product for your Agilent logic analyzer. WaveFormer Pro gives you the power to capture logic analyzer waveform data. Use your data to create simulation-ready HDL code or high quality timing diagrams for your design reviews. Or, use the timing analysis and simulation capabilities of WaveFormer Pro to debug your design faster and more efficiently. Simulation, debugging and documentation. Hey, what are friends for? Simulate and Visualize Activity on Internal Nodes

One of the most frustrating problems encountered when debugging a circuit is the inability to see what

is happening on all the internal signal nodes of an FPGA or ASIC. A logic analyzer can only show the

activity on signals that are brought out on device pins. Unfortunately, many designs are I/O limited.

Even when there are no limitations, there are almost never enough pins available to bring out all the

useful nodes.

Find Elusive Setup and Hold ViolationsWaveFormer’s simulation environment can generate a report of ALL setup and hold timing violations specified between any two signals in a timing diagram regardless of whether this signal is a captured waveform or a simulated waveform (logic analyzers typically only flag the first violation). Setup and hold time violations in ASICs and PLDs are particularly troublesome because the timing violations usually occur on flip-flop inputs that are not directly available at device pins, but are instead a logical function of the device’s inputs. Using conventional debugging techniques, these timing violations are extremely difficult to catch because they cannot be directly measured. WaveFormer’s ability to simulate internal signals makes it simple to detect timing violations between signals buried inside a chip. Document Circut OperationWaveFormer Pro can document circuit operation by converting captured waveform data into true timing diagrams. Add delay, setup, and hold timing parameters to document the temporal relationships between signal transitions. Finally, you can improve the readability of your timing diagrams by adding text and grid lines. When your timing diagram is complete, WaveFormer Pro can create publication quality WMF, MIF or EPS images for use in Word, FrameMaker or PDF files.

Common Agilent and HP Questions

WaveFormer Pro is available for Windows 95/98/NT, Solaris and HP-UX operating environments.

|

|

|