|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

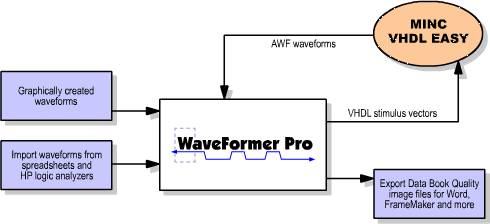

SynaptiCAD's WaveFormer Pro has the ability to generate stimulus vectors for MINC's VHDL EASY simulator. WaveFormer Pro lets you specify and analyze timing diagrams early in the design cycle, then take that same work and use it as stimulus for circuit simulation. With WaveFormer, users create timing diagrams by drawing signals, clocks, and buses, and by simulating Boolean and register logic signals. Graphical timing parameters like delays, setups, and holds actively move and monitor signal transitions. |

Import & Export WaveformsWaveFormer Pro supports waveform input from a variety of sources including: drawing waveforms graphically in the timing diagram editor, numerical input from a spreadsheet, waveforms captured by logic analyzers, and simulator output generated by MINC's VHDL EASY simulator. All WaveFormer waveforms can be exported as stimulus vectors for HDL simulators. WaveFormer Pro supports waveform input from a variety of sources including: drawing waveforms graphically in the timing diagram editor, numerical input from a spreadsheet, waveforms captured by HP's logic analyzers, and output generated by MINC's VHDL EASY simulator. All waveforms can be exported as astimulus vectors. |

VHDL & Verilog SupportSynaptiCAD provides two levels of VHDL and Verilog test bench generation. WaveFormer Pro produces single timing diagram stimulus generation, which is perfect for testing small designs and models. Additionally, WaveFormer's big brother TestBencher Pro generates multi-diagram, self-testing, reactive test benches. TestBencher Pro is perfect for building bus-functional models of microprocessor and bus interfaces. |

|

|

|

|