|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

TDML: An XML-based Interchange Standard for Waveforms and Timing SpecificationsOne of the most serious problems facing engineers during the creation of digital systems is the interchange of design and test data between different EDA tools and test systems. Frequently, data entered or produced at one stage of development must be completely discarded and manually re-entered because no exchange mechanism exists for converting data produced in one tool's format into a form acceptable to other tools. This problem is most evident in the variety formats for representing digital waveform and timing information. Waveform and timing parameter data is produced and distributed in many incompatible forms: timing diagrams in printed data sheets, test vector stimulus, tester pattern files, static timing analyzer reports, simulation dump files, logic analyzer data, etc. Each format has its own syntax and content requirements, generally preventing the exchange of even simple waveforms. Ad hoc converters have been written by many engineers to translate between individual formats, but due to the lack of a standardized intermediate format, this has meant a new set of translators must be written every time a new format is introduced in a design flow. To address this problem, an interchange format called Timing Diagram Markup Language (TDML) has been created that contains a superset of the information found in existing waveform and timing formats. TDML stores this data in a structured form that makes it easy for EDA tools and translators to extract only the portions of the data they need. TDML is also a human readable format, simplifying the creation and testing of TDML reader and writer programs. TDML is an XML-based format TDML is based on the eXtensible Markup Language (XML), which has been hailed as the "next generation" HTML for the Internet. There have been numerous articles written about XML in which the benefits are described in terms of merging of database and document concepts in order to efficiently manage large amounts of information. However, detemining how these benefits apply to engineering data and timing diagrams may not be completely obvious. For engineers, the most useful benefits of TDML's XML-basis are: (1) a highly structured, easily parsed format, (2) several freely available XML browsers and parsers exist that provide file validity checking and simplify the creation of TDML parsers, (3) the format provides a method for adding and preserving extra information in a TDML file that has not yet been defined in the standard without breaking the ability of other tools to read the "standard" TDML information. TDML is simple to parse because all the information is hierarchically organized and contained between begin and end tags (figure 2 shows a TDML code fragment with start and end tags surrounding a signal and its waveform). This structuring of the data and the fact that TDML is a text based format makes it easy for engineers to write export scripts to convert their waveform data to and from TDML. <signal id="ID2" show="1" show.grid="0">

<conn.ptr conn.id="ID1">SIG0</conn.ptr>

<waveform id="ID3" locked="0">

<e id="ID3V" driven="1" s="1" te="0" tl="0"></e>

<e driven="1" s="0" te="55000" tl="55000"></e>

<e driven="1" s="1" te="90000" tl="90000"></e>

<e driven="1" s="0" te="140000" tl="140000"></e>

<e te="190000" tl="190000"></e>

</waveform>

</signal>

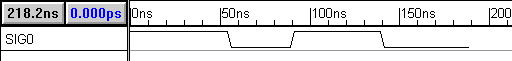

Figure 2: TDML code fragment with start and end tags surrounding a signal and its waveform. Below is the same waveform, when the TDML file is opened with WaveFormer Pro.

Several free XML parsers (with source code) are available, so TDML capability can easily be added by EDA vendors and test equipment manufacturers. One relatively unique aspect of XML-based versions of TDML parsers is that they can "validate" TDML files, guaranteeing that the TDML file contains data that meets TDML file format requirements for structure and content. This ability dramatically reduces the chance for the inadvertent creation of incompatible versions of TDML files as a result of a misreading of the TDML specification standard and provides a "confidence check" for TDML users. To make TDML a truly open standard, TDML supports a method for tools to ignore yet preserve information that they do not understand. That means that a waveform translator such as SynaptiCAD's WaveFormer Pro can write TDML files that include voltage threshold levels for generating SPICE files and VHDL and Verilog signal typing information for generating HDL test stimulus. Yet a simple timing diagram editor can still read the TDML file and ignore the information that it does not understand. Using the same methods, programs can store application specific information in their TDML files without having to worry about breaking other tools that need to read the basic TDML information contained in the files. History of TDML In November of 1996, SynaptiCAD learned that the SI2 standards organization was working on the development of an electronic data sheet standard called ECIX (Electronic Component Interchange and eXchange) and approached SI2 with a proposal to add a structured format for representing timing diagrams to the ECIX standard. Subsequently, SI2 issued a Request for Technology and as a result, the TDML Working Group was formed in December 1997 and the first version of the TDML standard was released in November 1998. ECIX members include a number of semiconductor manufacturers such as Hewlett-Packard, Hitachi America, IBM, Intel, Lucent, Motorola, National Semiconductor, Texas Instruments, and Philips Semiconductors. Most of these manufacturers have plans to begin distributing their component timing information over the web as TDML files to streamline delivery of component information and simplify import into EDA tools and test equipment. TDML and the IP industry Although the original impetus for the development of TDML was as an interchange format for timing diagrams that describe hardware components, TDML is equally at home describing "virtual" components such as intellectual property (IP) cores. One of the major challenges to using an IP core is to determine a method for communicating with the IP block. IP blocks communicate using transaction protocols that describe the rules that need to be followed in order for the block to function correctly. Transaction protocols have long been described using timing diagrams because they form a concise visual description of cause-effect relationships between signal events in a transaction. TDML-based timing diagrams can also specify the design constraints such as setup and hold time requirements that must be met by interacting components. Another important issue in IP usage is substitution of one IP block with another that is behaviorally equivalent either for higher performance, increased functionality, or simply because a design is being ported to a different process. Since timing diagrams focus on describing interface behavior rather than internal operation, they document the design requirements for IP use without dictating implementation details, simplifying drop-in replacement of IP blocks. TDML provides an open format for distribution of protocol specifications, enabling IP vendors to release complete interface information without tying their customer base to a specific EDA tool suite. An open format also encourages tool vendors to find new uses for TDML information, increasing the ultimate usefulness of TDML in the design process. Free Waveform and TDML waveform viewer available for download Although TDML is relatively new standard, both a free TDML viewer, WaveViewer, and an evaluation copy of a commercial TDML-based waveform translator, WaveFormer, are available for download from SynaptiCAD's web site at http://www.syncad.com. The free TDML viewer can also read waveforms in several other formats including HP logic analyzer data files and Verilog VCD files. The commercial waveform translator can import waveforms in any of these formats and translate them into stimulus files in a number of formats including VHDL, Verilog, SPICE, and HP digital pattern generator format. |

|

|