|

Main: VHDL2Verilog, or Verilog2VHDL

VHDL-Verilog Interoperability:

Will V2V translation tools work for me?

Is it really a bilingual World?

It is a bilingual world. The sooner you admit it, the better it is.

Traditionally, designers have concentrated on using one of the HDLs available (viz. VHDL or

Verilog) for design purposes. However, recent times have seen designers needing to work with both VHDL

and Verilog. This has created a strong need for VHDL-Verilog interoperability solutions.

Often times, designers are required to integrate legacy designs not available in the language of choice.

Another scenario: you may be a library developer, and are required to maintain designs in both languages.

Or you may be one of those people who wants to learn the other language, and see for yourself

what the HDL wars are all about.

If I have designs in both languages, what do I do?

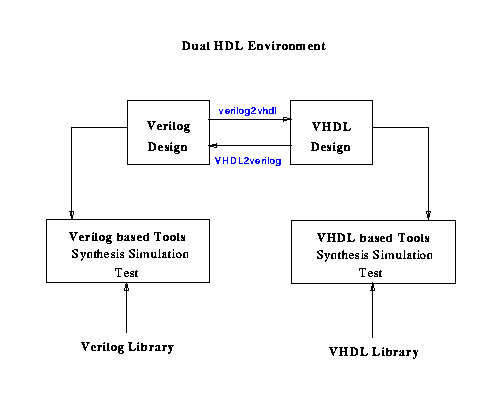

That is where we come in. See figure below:

Verilog2VHDL is a Verilog to VHDL translator, aiding you in moving your Verilog designs to VHDL.

VHDL2Verilog is the VHDL to Verilog translator. Using these translators, you can integrate your

designs in the preferred synthesis-simulation-test environment.

How do I know if the translators will really do the job for me?

Answer the following questions:

- Do you know the language you want to translate to?

- Do you write synthesizable code?

If you have answered yes to the above two questions, then yes, translators will solve your problem.

On the other hand, if you write simulation models, and want to translate testbenches and other non-synthesizable

code, translators will come in very handy with some manual editing of the output.

Will it do the job for me totally?

A push-button, no user-intervention-needed Verilog<=>VHDL translator is a myth. As a user,

you need to know what is going on, you may be required to edit the output to achieve full translation.

For most cases, there is a one-to-one mapping of constructs. For constructs not translated by the translator,

comments are inserted in the output code. Code generated by translators is very readable, with comments

in the input preserved.

Therefore, it is important to be prepared for manual editing of the output file, if the input so requires.

You can even register and get access to the complete documentation of the translators

(a list of supported constructs is included).

|