|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Next: The V2V Advantage, Main:

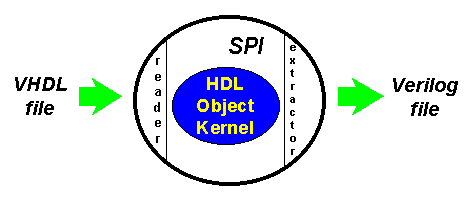

VHDL2Verilog Product DescriptionVHDL2Verilog translates hierarchical IEEE Standard 1076-87 and 93 VHDL to Verilog HDL. It translates all structural VHDL constructs, as well as a large subset of RTL VHDL constructs. Verilog that is created by VHDL2Verilog is functionally equivalent to input VHDL, and because of one-to-one mapping of VHDL to Verilog, is easy to understand. Syntax and semantic checking of the VHDL input is also performed during translation and output Verilog is compatible with any Verilog-XL compatible simulator. VHDL2Verilog is a valuable design reuse tool because it preserves the level of abstraction during translation. There is a one-to-one mapping of constructs in most cases. Because the abstraction level is preserved, Verilog can remain technology independent in cases where the input is behavioral or RTL. VHDL2Verilog can:

VHDL2Verilog is also available with an object-oriented Software Procedural Interface (SPI) to access the output HDL. VHDL2Verilog is shipping for Solaris, Linux, HP-UX, and Windows.

|

|

|