New Features in SynaptiCAD Tool Suite v16.0

All SynaptiCAD Programs

- Automatic checking for new software version

updates. Also manual checking available from the Help > Check for

Updates menu.

All Timing Diagram Editors (DataSheet Pro, WaveFormer Pro, Timing Diagrammer Pro)

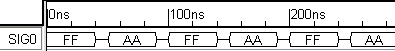

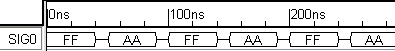

- Virtual states can now be set from waveform

equations controls in Signal Properties dialog for quick creation

of repetitive bus patterns (See Section 1.3 Generating Waveforms

and States with Equations). For example:

(40=FF 10=ZZ 40=AA 10=ZZ)*20

- New Waveform Block Equation function,

GetPrecedingRealValue, returns the state of the preceding event as

a real value suitable for analog equations. This is especially

important for creating waveform blocks that base their initial

Virtual state value from the Virtual state value immediately

preceding the block (see Section 8.2 Waveform Equation Blocks for

editable Analog waveforms).

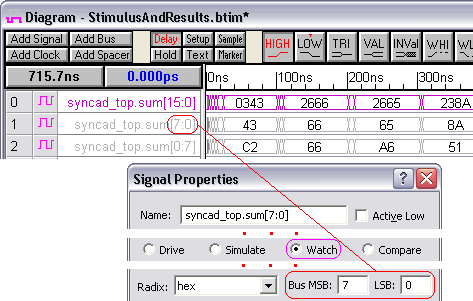

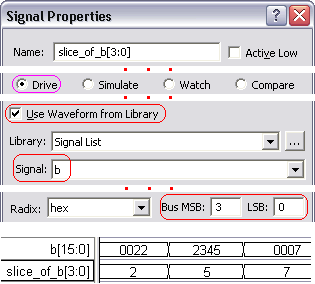

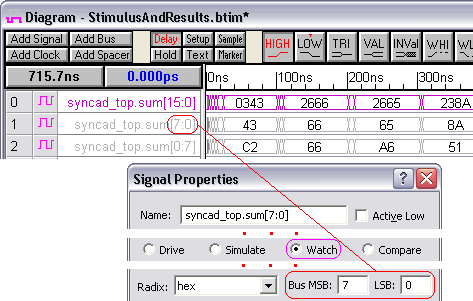

- Support for displaying bit slices of bus signals

in the Timing Diagram Editors (see Section 1.8 Referencing

Waveforms from Libraries). Just create a new signal, then use the

WaveForm From Library and choose the signal to slice into. Next set

the MSB and LSB to the section of the signal to view.

- New documentation for the BtimPython API, which

allows python scripts to read or write timing diagram (btim) files.

The documentation is located in the SynaptiCAD > Help > btim.html

file.

- A timing diagram's dirty flag is no longer

"aggressively" set (previously the dirty flag was set as soon as a

user left clicked in a diagram window). Now a timing diagram's

dirty flag is only set when the timing diagram is actually changed.

- Many miscellaneous bug/crash fixes.

- Improved crash reporting mechanism.

WaveFormer Pro and DataSheet Pro

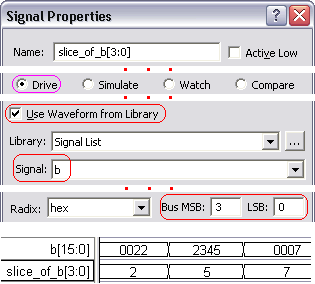

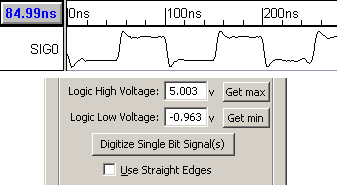

- Added import for Agilent's 16900 logic analyzer

csv file format (see Section 11.6 Agilent Logic Analyzer &

Oscilloscope - Import).

- Speeded up simulation waveform capture allowing

up to 8x faster simulation under GUI.

- Faster simulation log window and decreased

memory required for text editor and simulation log windows. This

speeds up simulations that output a lot of informational data to

the log window.

- Speeded up simulation under the GUI by reducing

overhead between simulator and GUI.

WaveFormer Lite Features

WaveFormer Lite is a less expensive and feature

limited version of WaveFormer Pro that works with 3rd party FPGA/ASIC

tool flows FPGA design environments including the Actel Libero

software.

- Added the ability to display Analog waveforms.

- New Project Window display in WaveFormer Lite that

allows specifying the Models Under Test (see Appendix C.1 WaveFormer

Lite Design Flow).

BugHunter Pro

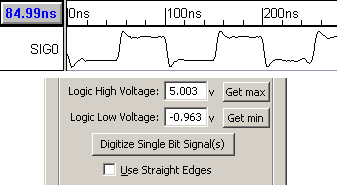

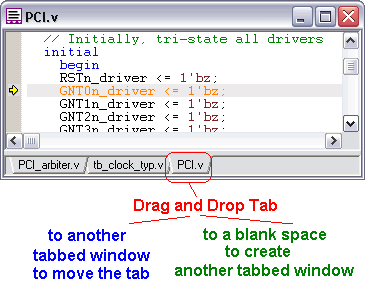

- While stepping through the code, new editors will

open in a new tab on the most recently active editor window.

- To move a tab to another tabbed window or the

Report window, drag and drop the tab to that window.

- To open a tab in a new tabbed window drag and drop

the tab to a space outside any other tabbed window (see the

BugHunter Manual: Section 4.1 Opening, Saving, and Creating New

Source Code).

- Added support for -g and -G options to BugHunter

Verilog preparser to allow the values of parameters in your source

files to be overridden at compile time. These options support both

absolute paths to a particular parameter and relative paths that

match to all instances in the design hierarchy. If an option has an

invalid value literal or wasn't found in the hierarchy, a warning

message will be issued (see the BugHunter Manual: 5.8 Simx Override

Parameter Values Options).

- Support for watching bit slices of simulated

signals. The bits can be reversed by making the MSB smaller than the

LSB. In the above diagram the [7:0] slice has a segment that is 'h43

('b0100 0011), and the [0:7] slice has a segment that is 'hC2 ('b1100

0010).

- Preparser can display "constant" values in project

window after project is built (prior to simulation). Particularly

useful for checking the computed values of VHDL generics and Verilog

params/localparams in large designs.

- Improved parsing of VHDL files when

packages/components are compiled into multiple VHDL libraries.

- Allow individual user source files to be compiled

into file-specific destination libraries(see the BugHunter Manual:

2.1 Build and Simulate).

- Added destination library management for Incisive

simulator (already supported for ModelSim/ActiveHDL/VCS).

- Speeded up adding/deleting lots of watched signals

(e.g. upwards of 10000 signals).

- BugHunter now supports the 64-bit versions of

Mentor's ModelSim and Cadence's Incisive. These simulators can now be

selected from the Simulator dropdown menu inside BugHunter.See Step 1

Setup the Simulator Path in the BugHunter and VeriLogger Manual.

- The BugHunter build and run commands also create

batch files with all the commands needed to build, elaborate, and run

the current simulator from the command line. These files can be used

to create regression test suites that run on different computers. See

Section 5.3 Batch Files for Command Line Simulators in the BugHunter

and VeriLogger Manual.

- SynaptiCAD Simulators: build_simx.sh, run_simx.sh, build_vlogcmd.sh

- Cadence Verilog: build_ncvlog.sh, elab_ncvlog.sh, run_ncvlog.sh

- Cadence VHDL: build_ncvhdl.sh, elab_ncvhdl.sh, run_ncvhdl.sh

- Mentor ModelSim Verilog: build_vlog.sh, run_vlog.sh

- Mentor ModelSim VHDL: build_vcom.sh, run_vcom.sh

- Synopsys: build_vcs.sh, run_vcs.sh

- When compiling using Cadence Incisive (i.e.

ncsim), BugHunter automatically creates a file called cds.lib in

the project directory that tells Incisive how to map symbolic

library names to physical directories on disk. This file also

includes a link to a file called cds_project.lib (also in the

project directory) where a user can add additional symbolic to

physical mappings if needed. See Section 5.3 Batch Files for

Command Line Simulators in the BugHunter and VeriLogger Manual.

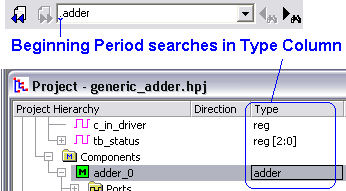

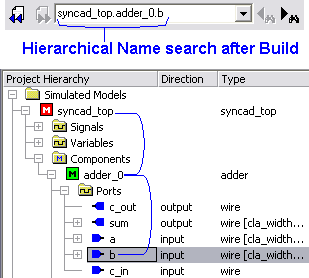

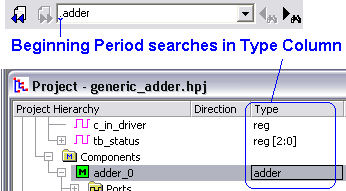

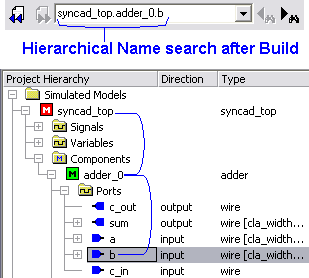

- Enhanced Text Search in the Project window: In

addition to the existing "generic" search, faster and more specific

searches can now be performed using "hierarchical search" and

"instance type search". These faster searches only search through

the "Simulated Model" portion of the project window, so you must

have previously built your design for these searches to function.

See Section 4.4 Searching in the Project Window in the BugHunter

and VeriLogger Manual.

- To search for all instances of a component put a

period at the beginning of the search string.

- Use hierarchical names to search for a specific object.

- Right click menu option in source edit window to

open Show Drivers dialog on the selected signal/variable.

- Major enhancements to information displayed in

Show drivers window.

- Previously only signal drivers could be

viewed, now all statements affecting registers are also

displayed, enabling full cause-effect tracing through the

entire simulation when simulating with Verilogger Extreme.

Note: when using BugHunter with supported 3rd party

simulators, Show Drivers can currently only show "signal

drivers" but not "register drivers" as the 3rd party

simulators don't support the necessary VPI interface

functions.

- Values of signals and variables in show

drivers window can now be changed from the show drivers

window by double clicking in the value column.

- Values in the Show drivers window that

have changed since the last pause in the simulation run

will be displayed with red text.

- Watch signals in diagram from the Show

Drivers dialog via right-click context menu. Watch either

a single signal or a signal's immediate driver signals.

- New right click menu functions in project tree

for setting the debugger interactive scope to the selected

instance and opening a source edit window to the instance or the

definition of that instance.

- Enable watching more signal types (e.g. VHDL

time and enum types) in ModelSim and Incisive.

VeriLogger Extreme Features (simx)

- Race Detection Options: When you want to check

for race conditions in your code, VeriLogger supports several

options that can be used to change the event queue order. If your

design passes with one ordering, but fails with another, this

indicates there is probably a race condition in your design. See

Section 5.10 Race Detection Options in the BugHunter and VeriLogger

Manual.

- --scd_invert_ queue inverts the default

order of executed processes.

- --scd_randomize_queue randomizes the default order of executed processes.

- --scd_mtilike_queue executes events in a similar order as ModelSim.

- --scd_immediate_sensitivity makes event

control statements at the beginning of a process immediately

sensitive after simulation initialization

- --scd_mtilike_dist_functions makes $random

and $dist_ functions behave like ModelSim when real-value

passed as the seed.

- New build optimizations (e.g. some cycle-based

optimizations, continuous assign collapsing) for faster runtime

performance.

- Runtime warnings generated for potential infinite

loops in user's Verilog code that allocate too much memory.

- Improved errors/warnings/messages/notes for calls to PLI routines.

- Support for vpiUse attribute (enables navigation of

cause-effect relationships in BugHunter via Show Drivers windows).

- New option, --scd_ncsimliketchkmsg, prints timing violation messages in NCSim format.

- Flags for ModelSim-Compatible Timing (see Section

5.7 Simx Specify block and SDF Timing Options in the BugHunter and

VeriLogger Manual):

- +pulse_path_e/error_percent: Sets

the percentage of delay for the pulse error limit only for

specify paths.

- +pulse_path_r/reject_percent/: Sets the

percentage of delay for the pulse reject limit only for

specify paths.

- +transport_path_delays: Specify path

delays will operate as transport delays (shorter pulses

will be propagated).

- Support for $countdrivers systf function.

- Support for ifnone iopaths.

VHDL2Verilog Features

- VHDLl2Verilog comes with the automated tool,

mapmaker, to help you quickly create map files. At a command

prompt, run mapmaker with the list of your source files, and it

will generate a vhdl2v.map file in the current directory which

contains mappings for all of the packages in those source files,

plus the default mappings. See Section 9.3 Mapping VHDL packages

to file locations in the BugHunter and VeriLogger Manual.

- Proper propagation of a range's direction flag

when constructing a discrete range that references another object.

- Return the subtype indication's range instead of

the range of the element type for arrays.

- Improved resolution of overloaded functions.

- Improved resolution of parameters in nested function invocations, e.g. f(g(x)).

- Added a new option -signed which translates the

IEEE.STD_LOGIC_ARITH.SIGNED data type to a Verilog 2005 'signed'

data type. Disabled by default.

- Added a new option -system_verilog to allow

translating VHDL blocks into SystemVerilog nested modules.

- More efficient memory utilization allows parsing

of very large input files.

Verilog2VHDL

- Added support for advanced format specifiers

(e.g. "%02d" in $display calls). Also allow macros as $display

parameters.

- More efficient memory utilization allows parsing of very large input files.

TestBencher Pro Features

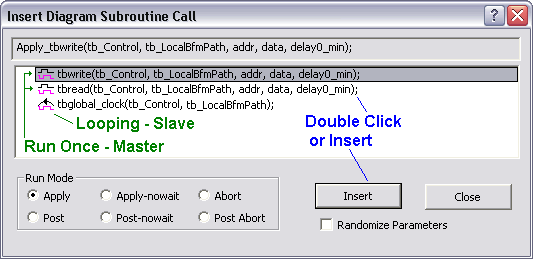

- IMPORTANT CHANGE FOR EXISTING VHDL CUSTOMERS:

We have changed the generic name tb_InstancePath, to the new

name, tb_LocalBfmPath. If you have legacy TestBencher projects

created before version 15.14a, you will need to change any Post

calls in your sequencer processes in these projects to use the

new variable name.

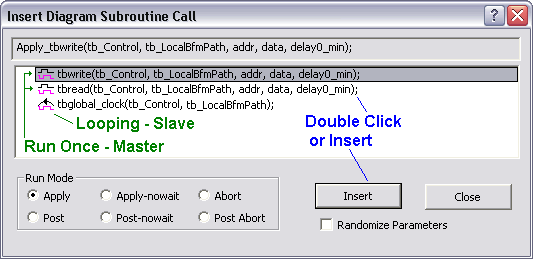

- Insert Diagram Calls dialog modified to allow

inserting Post calls as well as Apply and Abort calls. See the

TestBencher Pro manual Step 5: Define Sequencer Process.

- Ability to specify a destination library other than "work" for the generated testbench files.

- Automatically generates Use Library statements

inside the testbench if the MUT is stored in a different

library.

- Improved code-generation and associated

documentation for randomizing transactors in a BFM

(bus-functional model).

- Generate a default uniform random weighting

matrix for transactors in a BFM. See the TestBencher Pro manual

Section 7.6: TM fill from Random Generator.

- Added new PostRandomTransactionType call for

randomly generating a single transaction based off the random

weighting matrix. See the TestBencher Pro manual Section 7.6: TM

fill from Random Generator.

- Improved display of TestBencher-generated log reports during simulation.

Improved Optional Features

- Speeded up waveform comparison engine.

- Store all print settings in diagram views for better OLE image embedding.

UNIX

- Changed default font in simulation log window to speedup scrolling (12x faster) when using a remote X server.

- Improved online help display under web browsers and new functions for navigating the help files.

- General GUI improvement (fonts, dialogs, buttons, etc).

New Features pages for previous versions:

List of Features in Version 15.0

List of Features in Version 14.0

List of Features in Version 13.0

List of Features in Version 12.0

|