|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

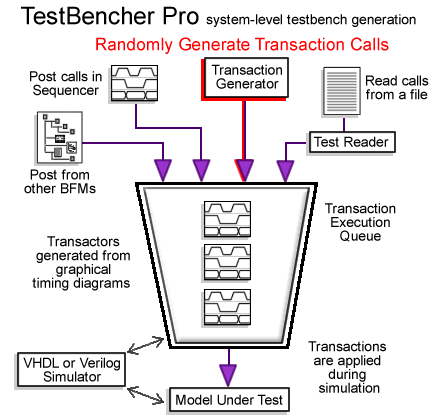

| Product Update Press Release, March 28, 2011 TestBencher Simplifies Random Transaction GenerationSynaptiCAD has released a new version of TestBencher Pro, a VHDL and Verilog system-level testbench generation software that dramatically simplifies the process of creating and applying random bus transactions to RTL and gate-level models. The new version also simplfies creation of testbenches that reside in a different compiled library from the design being tested. TestBencher includes an updated version of SynaptiCAD's graphical HDL debugger, BugHunter Pro, with new debugging features and improved support of ModelSim and Incisive simulators on Windows and Linux platforms.

For more information on TestBencher Pro see the TestBencher Pro Graphical Test Bench Generation page. Randomizes Data and Transaction SequencingThe new version of TestBencher eliminates many of the manual coding steps that were previously required to create a testbench that applies a set of weighted-random transactions with contrained-random input data to a model under test. A fully randomized testbench with uniform transactor weightings can now be created without manually writing a single line of HDL code, although the tool supports a mixed-approach of manual and automatically-generated testbench code. TestBench Generation MethodologyThe user graphically draws timing diagrams that represent the protocols for the testbench's transactions with time and state variables to indicate transaction input data. A transactor is generated for each timing diagram and these transactors can be triggered by function calls made by the user in a testbench "transaction sequencer" process. The user can then selectively insert these calls into the sequencer process using a dialog that lists all available transactor function calls along with buttons to control how the transaction is applied. Using this dialog, transactions can be applied sequentially or concurrently, transaction can be scheduled on a queue for later execution, and the input data to the transactions can either be directly specified (via hard-coded values or pulled from a data structure) or randomly generated. After the user has finished generating his testbench, he can launch his HDL simulator from inside TestBencher using the contained BugHunter debugger to begin applying transactions to his design model. As each transactor executes, it captures the response from the design model and compares the response against an expected response. TestBencher supports both protocol checking and scoreboarding of transaction payloads using graphical constructs in the timing diagram to verify timing and payload data, with captured data values being stored in user-selected data structures (arrays, associative arrays, data files, etc). Pricing and AvailabilityTestBencher Pro is availiable now on all major Windows and UNIX systems. Contact SynaptiCAD for pricing on node-locked and floating versions. Marketing ContactFor any questions concerning this press release, please contact Donna Mitchell at 540-953-3390 or email at [email protected]. High-resolution images can be downloaded directly from SynaptiCAD's web site at www.syncad.com. |

|

|