|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

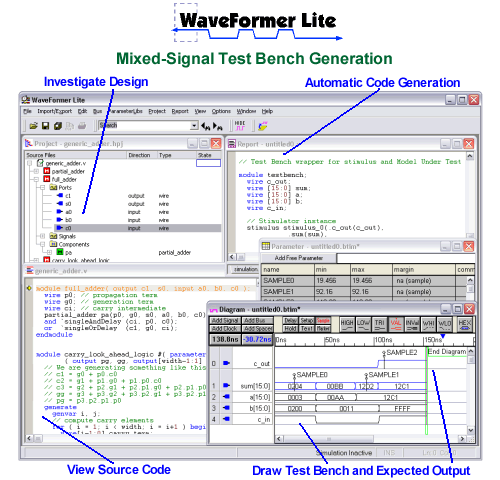

| Product Update Press Release, August 11, 2010 WaveFormer Lite Generates Mixed Signal HDL Test Benches for all FPGA design flowsSynaptiCAD has just released a major upgrade to WaveFormer Lite, it's entry level tool for generating VHDL and Verilog test benches graphically from timing diagrams drawn by the user. Previously only available as part of the Actel Libero package, WaveFormer Lite can now be purchased directly from SynaptiCAD. WaveFormer Lite generates native VHDL and Verilog testbench code, so it's compatible with all FPGA/ASIC vendors and tool flows without requiring any special runtime engines. The new version of WaveFormer Lite adds support for displaying analog waveforms, automatically generating analog and digital waveforms from editable waveform block equations, a syntax-coloring editor for VHDL and Verilog, and a new hierarchical project window that enables navigation thru the user's design.

For more information on WaveFormer Lite see the WaveFormer Lite Product Page. WaveFormer Pro Upgrade PathWaveFormer Lite licenses can be upgraded to WaveFormer Pro which includes waveforms generated from Boolean and Registered logic equations, min-max timing analysis, and support for more input and export formats including Tektronix and Agilent test equipment . Marketing ContactFor any questions concerning this press release please contact Donna Mitchell at 540-953-3390 or email at [email protected]. High-resolution images can be downloaded directly from SynaptiCAD's web site at www.syncad.com. |

|

|